ADSP TS201链路口通信的FPGA实现

发送模块:当外部接收到128位并行数据Datain(127:0)及FIFO写控制信号Datan_we后,将数据按以下规则重新组合排序:本文引用地址:http://www.eepw.com.cn/article/192061.htm

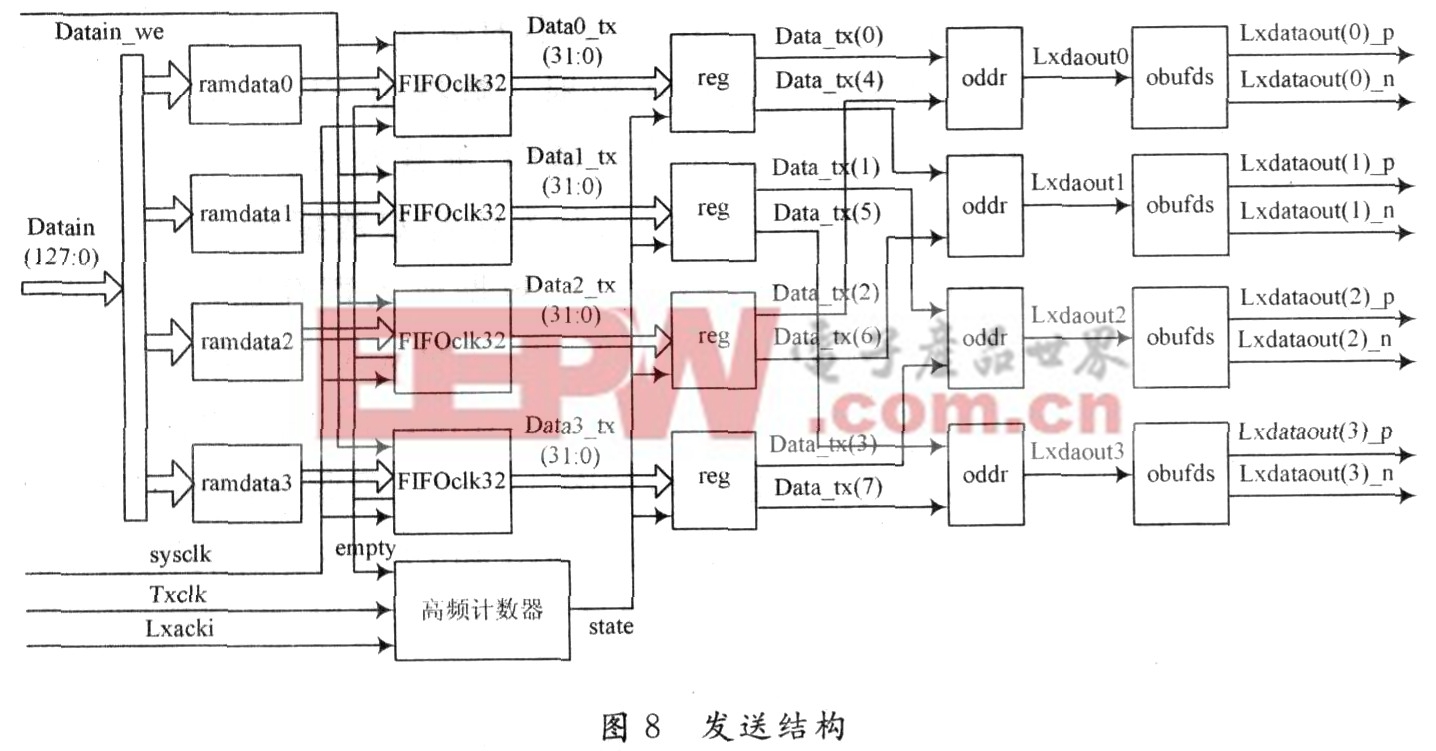

数据整理后,同时送入4个32位FIFO 32中,写时钟为sysclk。当FIFO 32不为空且Lxacki信号为高电平时,接收端允许传送数据。数据由FIFO 32中读出,分别放入4个32位寄存器中,准备发送。

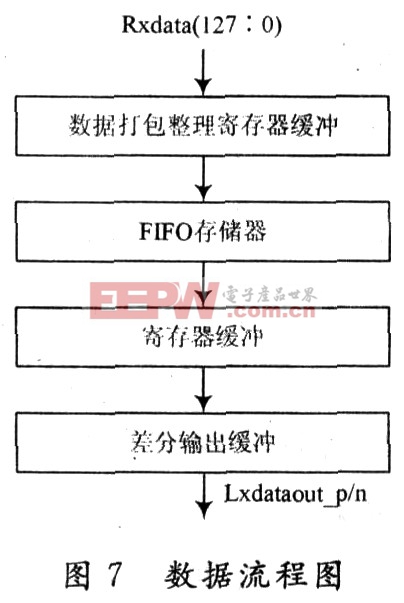

发送缓冲:此部分由状态机和双数据率(DDR)寄存器组成。当发送条件成立,数据放入寄存器后,由state信号控制寄存器,每个Txclk周期从4个寄存器中各读出2位数据Data_tx(7:O)共8位,为了满足链路口通信协议,发送出的数据应如图4所示。因此,将Data_tx两两分组(0和4,1和5,2和6,3和7),4对数据分别由4个双数据率(DDR)寄存器经差分转换送出,根据协议同时送出相应的时钟控制信号Lxclk p/n(与Tkclk相同频率)。按照协议,Lxclk的第一个上升沿必须在第一位数据传送中建立,因此,这里引入时钟信号Txclk90(Txclk相移90°),用来控制Lxelk p/n信号。数据传送结束前的最后一个时钟周期内将Lxbcompo信号置低(低有效)。发送(Tx)流程如图7所示。结构如图8所示。

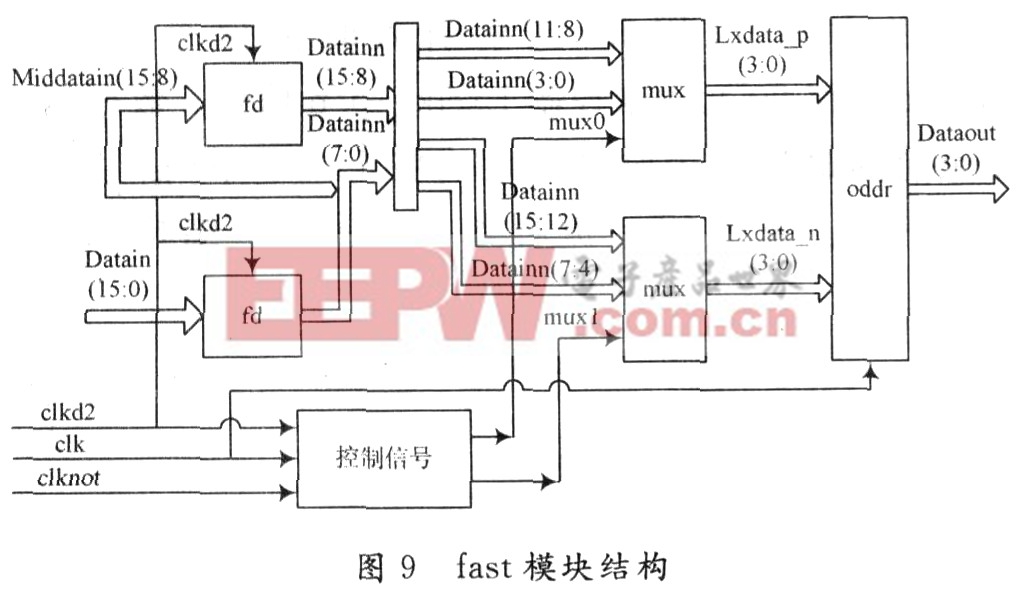

综合后此电路的主时钟Txclk频率最快可达到280 MHz。分析后发现此结构制约速度的瓶颈为高频计数器,此计数器产生控制信号。因此,为了提高速度优化结构。将此计数器改为原时钟的二分频信号clkd2控制计数。此时每当clkd2上升沿从FIFO 32读出32位数据放入寄存器,该寄存器同样由clkd2控制,时钟的上升沿来到时读出4位数据,组成连续的16位数据,这些数据经过子模块fast的处理,按照链路口协议要求输出数据dataout。综合后此电路的主时钟Txclk频率最快可达到400 MHz。

子模块fast的结构如图9所示。

评论