基于LEON3处理器和Speed协处理器的复杂SoC设计

前言

本文引用地址:https://www.eepw.com.cn/article/191992.htm随着科技的发展,信号处理系统不仅要求多功能、高性能,而且要求信号处理系统的开发、生产周期短,可编程式专用处理器无疑是实现此目的的最好途径。可编程专用处理器可分为松耦合式(协处理器方式,即MCU+协处理器)和紧耦合式(专用指令方式,即ASIP),前者较后者易于实现,应用较广。本文就是介绍一款松耦合式可编程专用复杂SoC设计实现,选用LEON3处理器作为MCU,Speed处理器作为Coprocessor。

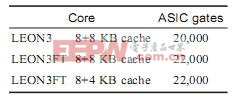

LEON3是由欧洲航天总局旗下的Gaisler Research开发、维护,目的是摆脱欧空局对美国航天级处理器的依赖。目前LEON3有三个版本(如表1),其中LEON3FT(LEON3 Fault-tolerant)只有欧空局内部成员可以使用。LEON3 (basic version)是遵循GNC GPL License的开源处理器,和SPARC V8兼容,采用7级Pipeline,硬件实现乘法、除法和乘累加功能,详细特性请参考相关技术文档[1]。

表1 LEON3的不同版本

目前,LEON3处理器因为开源、高性能、采用AMBA总线易扩展及软件工具完备等因素,在国内外大学(如UCB、UCLA、Princeton University等)及科研院所的科研活动中得到广泛应用。

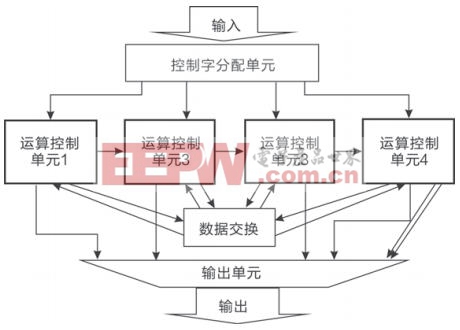

Speed(又名GA3816)是一款我国自主研发、处于同时代国际先进水平、可重构、可扩展的面向FFT、IFFT、FIR及匹配滤波应用的信号处理器,其内部结构如图1所示,具有以下特点[2~4]:

1)Speed在追求运算速度的同时兼顾通用性,通过设置64位控制字,器件内部资源可根据不同应用进行重组;

2)可以实现FFT、IFFT、FFT-IFFT、FIR、滑窗卷积等运算,峰值运算能力达256亿次浮点乘累加/秒;

3)由160个实数浮点乘法累加运算器组成40个复数乘法累加器阵列,1Mbit的双口SRAM,8个512×32bit系数ROM,两个直角到极坐标转换电路,两个对数变换电路及其它辅助电路和控制电路。

图1 Speed的内部模块结构

Speed传统的工作方式是通过片外FPGA输入控制信号和待处理数据,这不仅增大了PCB板级布线、调试的工作量,而且FPGA不能用C等高级语言编程,算法改动起来不灵活。另一方面,随着半导体工艺、微电子技术的发展,大规模的复杂SoC实现技术逐渐成熟,因此有必要将板级FPGA + Speed改进为芯片级MCU + Speed,这样既能实现真正的可编程增大灵活性,又能加快用户开发信号处理系统的速度。

评论