基于LEON3处理器和Speed协处理器的复杂SoC设计

利用AHB实现通信

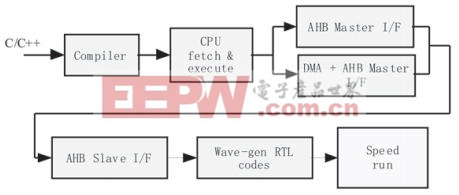

为了实现可编程,需要将C/C++程序表达的信息经过编译器、LEON3处理器、AHB总线、DMA控制器和必要的HDL代码,转化成Speed能够识别的信息,进入Speed模块中,如图2。其中AHB总线是LEON3 Core和Speed Core结合的关键。

图2 实现软件可编程的过程

AHB总线及AHB控制器

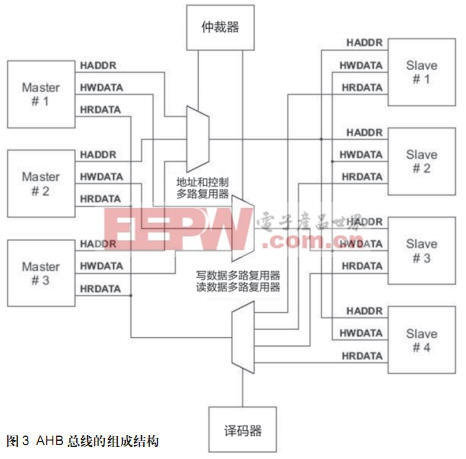

AMBA总线是一种应用广泛的层次化总线结构,有高速的AHB和低速APB之分,其中AHB是一种流水式高速总线结构,地址和数据总线相互独立,可挂载16个Master和Slaver设备,常用来组织和连接高性能模块,如处理器、DMA控制器、协处理器等[5~7]。AHB总线的核心是AHB控制器,主要包括仲裁器,译码器和多路复用器,其中仲裁器选择AHB Master,而译码器选择AHB Slave,实现写数据WDATA和读数据RDATA分开,如图3所示。

DMA控制器

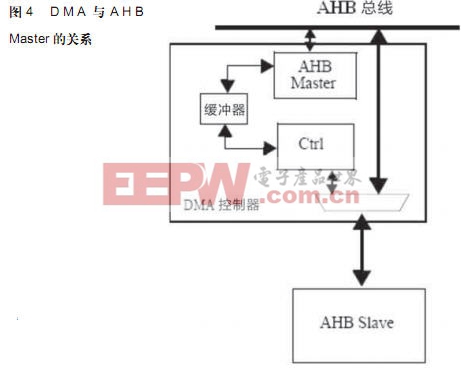

DMA是指设备直接对计算机存储器进行读写操作的方式。这种方式下数据的读写无需CPU执行指令,也不经过CPU内部寄存器,而是利用系统的数据总线直接在源地址和目的地址之间传送数据,达到极高的传输速率。DMA控制器一方面可以接管总线,即可以像CPU一样视为总线的主设备,这是DMA与其它外设最根本的区别;另一方面,作为一个I/O器件,其DMA控制功能正式通过初始化编程来设置。当CPU对其写入或读出时,它又和其它的外设一样成为总线的从属设备。

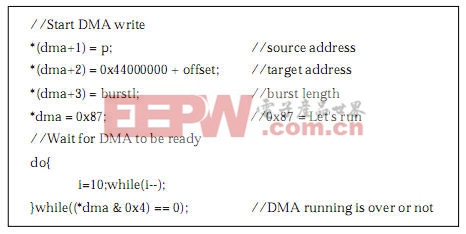

本文中为了实现DMA和AHB密切配合,即启动DMA后大量原始数据通过AHB总线从数据存储器进入Speed模块,需要DMA控制器内部包含AHB Master模块,如图4所示。另外需要说明的是,LEON3为了实现AHB上设备的plugplay需要在0xFFFFF000-0xFFFFF800地址空间添加设备信息[8~9],所以DMA 控制器和Speed协处理器亦要如此,以便LEON3的软硬件协调一致。在C语言实现DMA时,向DMA的控制寄存器写入相应的信息,即可启动DMA传输,如图5所示。

图5 启动DMA的C代码示意

Speed的AHB接口

评论