基于FPGA的高速定点FFT算法的实现

引 言

快速傅里叶变换(FFT)作为计算和分析工具,在众多学科领域(如信号处理、图像处理、生物信息学、计算物理、应用数学等)有着广泛的应用。在高速数字信号处理领域,如雷达信号处理,FFT的处理速度往往是整个系统设计性能的关键所在。

针对高速实时信号处理的要求,软件实现方法显然满足不了其需要。近年来现场可编程门阵列(FPGA)以其高性能、高灵活性、友好的开发环境、在线可编程等特点,使得基于FPGA的设计可以满足实时数字信号处理的要求,在市场竞争中具有很大的优势。

在FFT算法中,数据的宽度通常都是固定的宽度。然而,在FFT的运算过程中,特别是乘法运算中,运算的结果将不可避免地带来误差。因此,为了保证结果的准确性,采用定点分析是非常必要的。

1 FFT算法原理

FFT算法的基本思想就是利用权函数的周期性、对称性、特殊性及周期N的可互换性,将较长序列的DFT运算逐次分解为较短序列的DFT运算。针对N=2的整数次幂,FFT算法有基-2算法、基-4算法、实因子算法和分裂基算法等。这里,从处理速度和占用资源的角度考虑,选用基-4按时间抽取FFT算法 (DIT)。对于N=4γ,基-4 DIT具有log4N=γ次迭代运算,每次迭代包含N/4个蝶形单元。蝶形单元的运算表达式为:

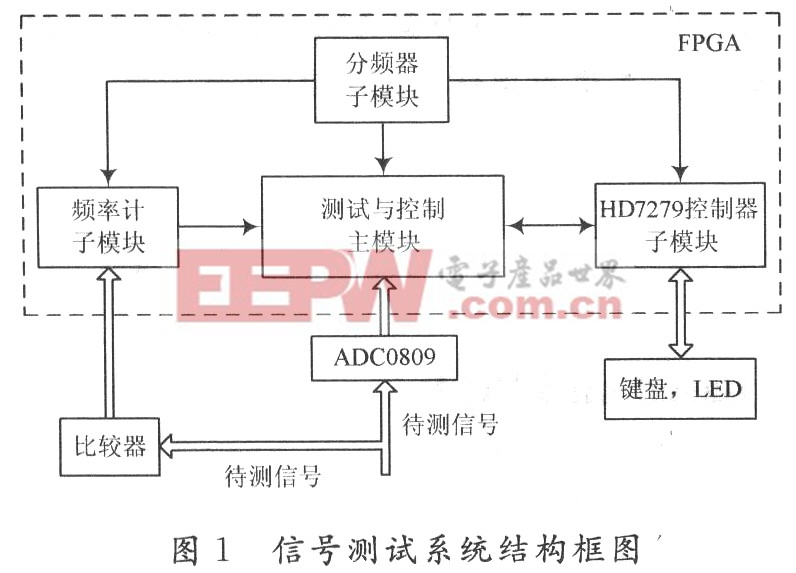

其信号流如图1。式中:A,B,C,D和A′,B′,C′,D′均为复数据;W=e-j2π/N。进行1次蝶形运算共需3次复乘和8次复加运算。N=64 点的基-4DIT信号流其输入数据序列是按自然顺序排列的,输出结果需经过整序。64点数据只需进行3次迭代运算,每次迭代运算含有N/4=16个蝶形单元。

2 FFT算法的硬件实现

2.1 流水线方式FFT算法的实现

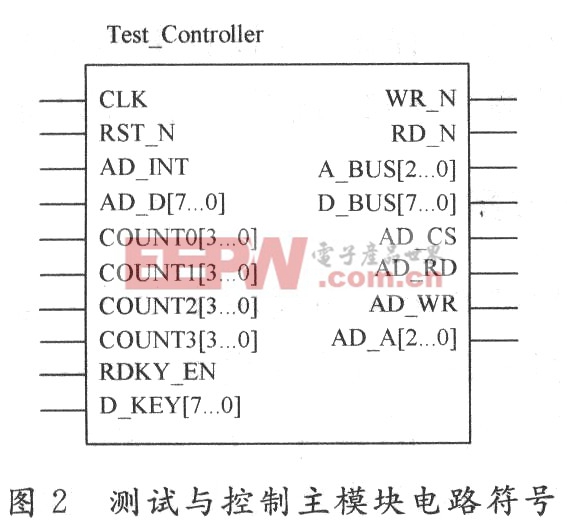

为了提高FFT工作频率和节省FPGA资源,采用3级流水线结构实现64点的FFT运算。流水线处理器的结构如图2所示。

评论