基于FPGA的自适应锁相环设计

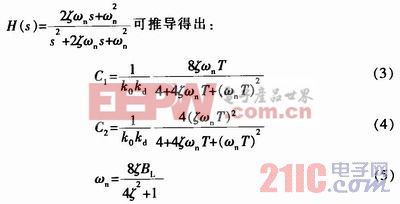

式中,ωn、T分别对应锁相环的自然角频率和环路调整时间间隔,可根据系统要求进行取值,设计中取T为采样时间间隔,即每个点调整一次,ζ取常用值 0.707,ko、kd分别对应鉴相增益和相位控制灵敏度,BL表示环路噪声等效带宽。由式(3)~式(5)可知,噪声等效噪声带宽BL和环路滤波器系数 C1、C2一一对应,因此改变噪声带宽即可通过调整系数C1、C2实现。传统锁相环中,取固定值,一般选取满足条件BL≤ O.1Rb的值,其中Rb为信息数据速率。

4.2 系数调整

相干解调系统中,同步系统的相位误差直接影响着系统的误码性能,其对应关系为:,其中ψ为相位误差。因此噪声水平较高时,应该尽可能减小噪声带宽,近而减小ψ值,噪声水平较低时,适当增加噪声带宽,加快跟踪速度。

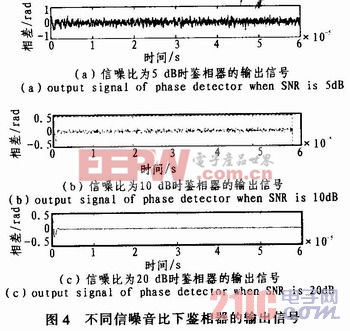

利用仿真软件MATLAB对3种噪声水平下的输入信号进行相位跟踪仿真,3种情况下,锁相环参数相同,输入的调制信号相同,不同的是对信号叠加3种功率不同的噪声。结果显示,锁相环中引入的噪声越大,则鉴相器模块输出信号的抖动越大。输入信号的信噪比为5、10和20 dB时,鉴相器模块的输出信号如图4所示。

由图4可以看出,噪声水平越高,则鉴相器的输出信号抖动越厉害,于是设计中利用鉴相器输出信号的抖动状况来判断锁相环中的噪声水平,并根据噪声水平来调整 C1、C2值。MATLAB仿真结果显示,鉴相器的输出值是在0值上下浮动,因此利用FPGA实现此功能时,可利用鉴相器输出值的绝对值或平方值判断噪声大小,浮动越大则噪声水平越高。利用单个点的抖动来判断时,具有一定的偶然性,结果不准确,容易产生误判,因此,在FPGA硬件板上利用VHDL编程实现时,对鉴相器的输出数据取绝对值或进行平方处理,并对连续15个点的绝对值或平方值进行累加运算,利用累加的结果来判断相位抖动的大小。对15个点取和时,利用树形加法结构,引入流水线设计方法,使各个加法器并行工作,确保输出结果的速率和输入数据的速率相等。计算过程中使用绝对值代替平方值,能获取与平方值相似的结果,有效降低运算量。进行带宽调整时,可以利用当前应该设置的BL值计算出与之对应的环路滤波器系数C1、C2由式(3)~式(5)可以看出,通过BL计算C1、C2时比较复杂,涉及多次除法运算、乘法运算以及加法运算,在FPGA中,实现除法器、乘法器都是比较占用逻辑资源的,因此设计中不采用直接计算的方法,而是利用查找表法来实现,首先订制2个容量为256的ROM,将可取的带宽值平均划分为256等分,对每个带宽值对应的C1、C2 值预先进行计算,计算结果经量化处理后,以MIF文件的形式分别加载到ROM1、ROM2。ROM1、ROM2的地址线均为8位设计中连接到同一信号,对应地址范围为0x00到OxFF,由图2中的噪声评估模块产生。噪声评估模块输出的初始值设置为0x7F,即初始带宽值设置为可取范围段的中间值,之后根据噪声评估模块的结果,与提前设定的上限值、下限值进行比较,并根据比较结果调整带宽值,其中上限值、下限值通过仿真得出,这两个域值与FPGA实现时采用的位宽、位截短处理、滤波处理等有关。为防止过于频繁地进行调整,程序中设定,如果连续3次的抖动高于上限值且当前地址值大于Ox00,则减小带宽值 (即地址减1),相反,若连续3次的抖动低于下限值且当前地址值小于0xFF,则增加带宽值(即地址加1)。

评论