基于FPGA和TMS320DM642的CCD图像采集和处理系统硬

当CCD产生的视频信号为模拟信号对,对其直接传输、存储和处理比较困难,须要将模拟视频信号转换为数字视频信号,以便对其进行处理,并进行高效可靠的传输和存储。当前,数字图像采集和处理系统不仅要面临高速宽带、高精度的挑战,而且对采样时机、采样点数、采样速率的可控性也提出了较高的要求,本文提出了一种实时图像采集和处理系统的设计方法,该系统以TMS320DM642[1-2]为核心,结合视频解码芯片SAA7115H和OSD FPGA构成实时图像采集和处理系统电路。

1 系统总体设计

1.1 系统结构

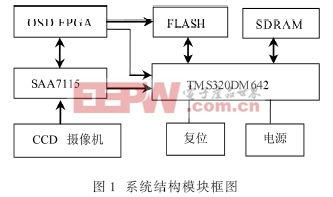

本系统以TMS320DM642为核心,采用模块化设计思想,整个系统主要由视频解码芯片(A/D转换芯片)、可编程逻辑门阵列(OSD FPGA)、TMS320DM642及外围电路组成。外围电路主要包括CCD摄像机、SDRAM图像存储器、FLASH程序存储器及TMS320DM642外围电路(复位、电源连接等)。图1为该系统的结构框图。

1.2 系统工作原理

由CCD摄像头摄入的PAL制图像传送到SAA7115解码器,SAA7115解码器将信号转变成并行的BT.656图像码流送至TMS320DM642视频口VP0,TMS320DM642将其再解码,得到YUV(4:2:2)格式的图像,并通过EDMA传输到动态存贮器(SDRAM)中存储,图像大小为每场720×288(宽×高),每帧720×576(宽×高)。CPU通过访问SDRAM中的图像数据,依照相应的程序进行相应的图像处理。

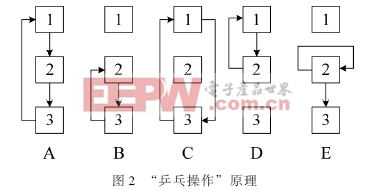

在实时图像处理系统中,为了不影响数据处理速度,需要在恒速的CCD图像采集与变速的TMS320DM642图像处理之间加入缓冲电路,缓冲采用TMS320DM642视频口的片内FIFO和片外SDRAM的乒乓缓存结构。“乒乓操作”是一个经常应用于数据流控制的处理方法,如图2所示,其处理流程为:输入数据流通过指针等时地将数据流分配到数据缓冲区1、2和3中,在第1帧的时间,将输入的数据流缓存到1;第2帧将输入的数据流缓存到2,与此同时,将1的数据作运算处理。在下个缓冲周期,再次切换,将输入的数据流缓存到3,与此同时,将2的数据运算处理。如此循环,A、B、C、D、E为其5种状态。

乒乓操作的最大特点是按节拍、相互配合地切换,将经过缓冲的数据流不停顿地进行运算及处理。把乒乓操作模块当作一个整体,此模块两端的输入数据流与输出数据流均是连续不断的,没有任何停顿,因此非常适合进行流水线式处理,完成数据的无缝缓冲与处理。

2 功能模块设计

2.1 视频采集模块

本系统采用Philips公司的SAA7115视频解码芯片将CCD模拟视频进行数字化,然后传给TMS320DM642的视频端口进行处理,同时分离水平同步(XRH)和垂直同步(XRV)等信号。

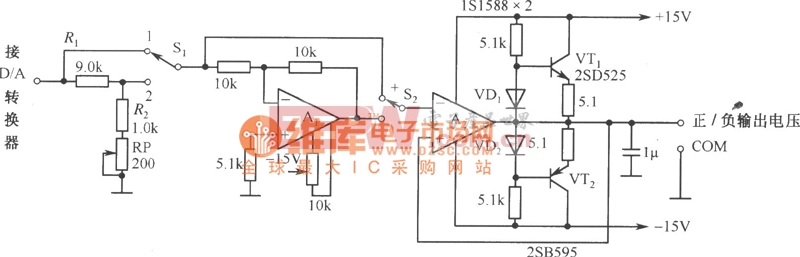

视频解码芯片采用SAA7115,省去时钟同步电路的设计,简化接口电路,提高系统的可靠性。由摄像机采集到的模拟信号经过视频端子进入到解码器SAA7115的模拟端Al11,经模拟处理和A/D转换后产生数字色度信号和亮度信号,分别对其进行处理。亮度信号处理的结果一路送到信号处理器,进行综合处理,产生Y和UV信号,经格式化后采用4:2:2 YUV格式从IPD[7-0]输出直接连接到TMS320DM642视频口的VP0[9-2]管脚;另一路经过同步分离器,由数字PLL产生相应的同步信号与TMS320DM642的VP0CTL0和VP0CTL1相连,同时PLL驱动时钟发生器,产生27 MHz的时钟同步信号LLC,输出到TMS320DM642的VP0CLK0管脚。解码器SAA7115与TMS320DM642的视频接口的原理如图3所示。

评论