基于FPGA的自适应锁相环设计

摘要:利用锁相环进行载波跟踪是获取本地载波的一种重要方法,针对锁相环的噪声性能和跟踪速度不能同时达到最优的限制,在锁相环PLL中引入自适应模块,根据环路所处的环境自适应对PLL环路参数做出调整。设计中利用仿真软件MATLAB对自适应锁相环进行仿真,并在FPGA硬件板上利用 VHDL编程实现。在栽波信号为10 MHz、采样率为80 MHz的条件下,设计的自适应锁相环在噪声水平较小时跟踪速度提高了0.5μs左右,在噪声水平较高时相位抖动降低了0.01 rad左右。

关键词:相干解调;PLL;FPGA;EP3C10F256C8

对于相位调制信号,相干解调为平均误码率最小的信号接收方式。相干解调需要在本地产生与接收载波信号同频同相的载波副本,锁相环是相干解调系统中获取本地载波副本时常用的方法。对于锁相环,噪声水平和跟踪速度是两个非常重要的性能参数,二者均取决于环路带宽但是不能同时达到最优。传统锁相环往往根据估算预先确定一个带宽值,因而当噪声环境发生变化时,该值可能不是最优值,甚至不适

合当前环境。在传统锁相环的基础上引入了自适应调整模块,根据当前环境自适应调整带宽值,确保无论锁相环处于固定或变化的噪声环境中均能工作在比较合适的带宽下,获取较好的跟踪效果。

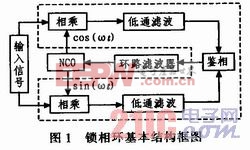

1 同相正交环结构

平方环和同相正交环都是解调系统中常用的跟踪环路,平方环的工作频率较高,对器件的性能要求较高,且平方环可能存在“理想平方器”的问题。如果同相正交环中的环路滤波器与平方环中的环路滤波器相同,则二者是等效的,同相正交环的环路中信号频率较低,对器件的性能要求较低,因此设计中选用同相正交环。同相正交环主要由误差提取模块、数控振荡器(NCO)和环路滤波器组成,如图l所示。图中虚线框为误差提取模块,用来鉴别本地振荡信号与接收信号的载波分量之间的相位差。环路根据提取出的相位差信号,不断调整本地NCO,最终使本地NCO和输入信号的载波分量同频同相,并在此基础上对接收信号进行有效地相干解调。

2 NCO实现及性能分析

NCO常用在直接数字合成器(DDS)中作为其数字实现部分。由此方法设计的DDS具有转换时间短、分辨率高、低相噪和输出相位连续等特点。在锁相环中,NCO用于产生本地振荡信号,由NCO同时产生本地的正弦及余弦信号。该模块由频率控制加法器、频率控制累加寄存器和波形存储器组成。输入的频率控制字在时钟信号的驱动下进行累加,利用累加结果作为地址在波形存储器中读取预先存储的正弦波数据。模拟锁相环中,由模拟压控振荡器产生的本地正弦信号和余弦信号往往不能严格正交,利用数字方法实现的NCO时可以较好地解决这一问题,只需正确设置正弦信号和余弦信号对应的初始地址即可。频率控制字f_con与输出f_out的关系为,其中fs表示采样频率,系统中为80MHz,2N为波形存储器的容量,N对应着该存储器的输入地址线的位数。

对于NCO,其性能主要体现在最小相位误差和最小频率分辨率上。波形存储器中通常存储一个周期的正弦波,因而最小相位误差为:。通过该式可以看出,N值取得越大,最小相位误差越小。然而N越大,对应的存储器容量越大,必然占用更多的逻辑资源,因而不能无限制地增加N值。设计中N取12,对应最小相位误差为0.0015 rad。NCO的最小频率分辨率为,其大小取决于频率控制字的位数,为了有效增加频率分辨率,取NCO的频率控制字位数M稍大于N,设计中取M为16。

评论