基于FPGA的自适应锁相环设计

3 鉴相方法及性能分析

如图l所示,鉴相模块是锁相环

的核心模块之一,其精度和鉴别范围直接影响锁相环

的核心模块之一,其精度和鉴别范围直接影响锁相环 的性能。系统接收信号为双相移相键控(BPSK)信号,设输入信号为s(t)=A(t)cos(2πfct+φc(t)),本地载波信号为。将输入的BPSK调制信号与NCO产生的2路本地载波信号分别进行相乘处理,对产生的乘积信号分别进行低通滤波,去除高频信号。为保持信号的线性相位及系统的稳定性,可采用有限冲激响应(FIR)滤波器完成低通滤波处理。通过低通滤波处理去除高频分量后,得到

的性能。系统接收信号为双相移相键控(BPSK)信号,设输入信号为s(t)=A(t)cos(2πfct+φc(t)),本地载波信号为。将输入的BPSK调制信号与NCO产生的2路本地载波信号分别进行相乘处理,对产生的乘积信号分别进行低通滤波,去除高频信号。为保持信号的线性相位及系统的稳定性,可采用有限冲激响应(FIR)滤波器完成低通滤波处理。通过低通滤波处理去除高频分量后,得到

式中,Q(t)、I(t)分别为锁相环

环路的同相信号和正交相信号,其中。

环路的同相信号和正交相信号,其中。鉴相处理即是对上述信号进行相应处理以得到对应的相差信号。常用的鉴相方法有正弦鉴相法,2倍角正弦鉴相法,正切鉴相法和反正切鉴相法。其数学表达式分别对应为:sign(I(t))·Q(t),I(t)·Q(t),Q(t)/I(t)和arctan[Q(t)/I(t)]。鉴相法的线性度越好、鉴相范围越广,则相应的锁相环

可跟踪的频率范围越大。利用仿真软件MATLAB对上述4种鉴相法对应的锁相环

可跟踪的频率范围越大。利用仿真软件MATLAB对上述4种鉴相法对应的锁相环 进行仿真。仿真参数对应实际系统中设置的参数,即采样速率为80 MHz,接收信号中载波分量的频率为lO MHz。多次实验结果显示:随着起始频差的不断增加,2倍角正弦鉴相法对应的锁相环最先出现跟踪不上的情况,随后是正弦鉴相法对应的锁相环,最后是正切鉴相法和反正切鉴相法对应的锁相环。

进行仿真。仿真参数对应实际系统中设置的参数,即采样速率为80 MHz,接收信号中载波分量的频率为lO MHz。多次实验结果显示:随着起始频差的不断增加,2倍角正弦鉴相法对应的锁相环最先出现跟踪不上的情况,随后是正弦鉴相法对应的锁相环,最后是正切鉴相法和反正切鉴相法对应的锁相环。用FPGA实现上述4种鉴相器时,正弦鉴相法使用少量的逻辑语句即可实现,占用的逻辑资源较少;2倍角鉴相法需要使用一个乘法器模块,在逻辑资源的占用上比正弦鉴相法稍多一些;正切鉴相法可选用查表法或者坐标旋转数字计算机CORDIC方法,占用的逻辑资源较多;反正切鉴相法可使用CORDIC方法实现,占用的逻辑资源也比较多。设计中可根据系统的资源情况和性能要求在上述4种鉴相方法中进行选择。本文中设计的模块应用在基于FPGA的直序扩频接收机中,对资源占用具有比较严格的限制,考虑到正弦鉴相法已经能够满足当前系统的性能要求,因此选用正弦鉴相法。

4 自适应锁相环

噪声水平和跟踪性能是锁相环的两个重要性能参数,但是二者是相互对立的,锁相环处于噪声环境中时,环路带宽越大,跟踪速度越快,同时引入的噪声越多;环路带宽越小,引入的噪声越少,同时跟踪速度越慢。通过对锁相环的传递函数进行分析得出,锁相环的环路带宽取决于锁相环中环路滤波器的带宽,对环路滤波器的带宽进行调整即是对锁相环的带宽进行调整。实际应用中,锁相环处于噪声水平较低的环境中时,其参数跟踪速度更为重要,此时应尽可能增加环路带宽,相反,噪声水平较高时,获取较小的相位抖动更重要,此时应尽可能减小环路带宽,抑制噪声信号。设计中按照这一思路,引入噪声评估模块,根据当前环境中噪声的大小对环路滤波器的带宽进行自适应调整。自适应锁相环结构如图2所示,自适应锁相环在传统锁相环的基础上引入了噪声评估模块和系数调整模块。

4.1 环路滤波器

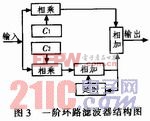

锁相环中的环路滤波器是一个线性低通滤波器,它主要有2个功能:1)滤除误差信号中的高频分量;2)为锁相环路提供一个短期的记忆,对环路的校正速度起到调节作用。模拟锁相环中的环路滤波器由电阻、电容和运算放大器等线性元件组成,如RC积分滤波器、无源比例积分滤波器、有源比例积分滤波器等等,数字环路中的环路滤波器可利用双线性变换和它们一一对应。设计中以有源比例积分滤波器为原型,通过双线性变换得到。锁相环的阶数比环路滤波器的阶数大1。环路滤波器的阶数越高,对应锁相环的跟踪性能越强大,二阶环路滤波器对应的三阶锁相环具有跟踪加速度频率输入的特性,对于本系统,二阶锁相环已经满足要求,因此采用一阶环路滤波器,与之对应的环路滤波器的数字化结构如图3所示。

图3中C1、C2为环路滤波器的系数,将此滤波器的传递函数引入锁相环,得出锁相环的传递函数,对照标准形式

评论