温度自适应性DRAM刷新时钟电路

动态存储器中的数据以电荷形式存储在电容中,因为MOS晶体管漏电,电荷会逐渐漏失,最终造成数据丢失。所以,动态存储器就需要不断对数据进行刷新,补充电荷。由于漏电流的大小受温度影响较大,导致电荷在存储器电容中的保持时间随着温度改变而改变。传统的刷新电路产生刷新信号的时钟周期是预先设计好的,固定不变,无法根据温度的变化自己调节周期,因此,传统的刷新电路设计的刷新时钟是基于高温的情况,刷新频率很快,这样就使得常温的时候刷新比较频繁,消耗大量功耗。

本文提出一种具有温度自适应的刷新时钟电路,其频率随着温度上升而上升。电路由基本的MOS管构成,利用了Diodes方式(二极管方式)连接的MOS管电流随温度变化的特点。电路不仅具有温度特性,降低了功耗,而且占面积小,与一般的CMOS工艺完全兼容,不需要工艺上的特殊处理。

1 电路结构

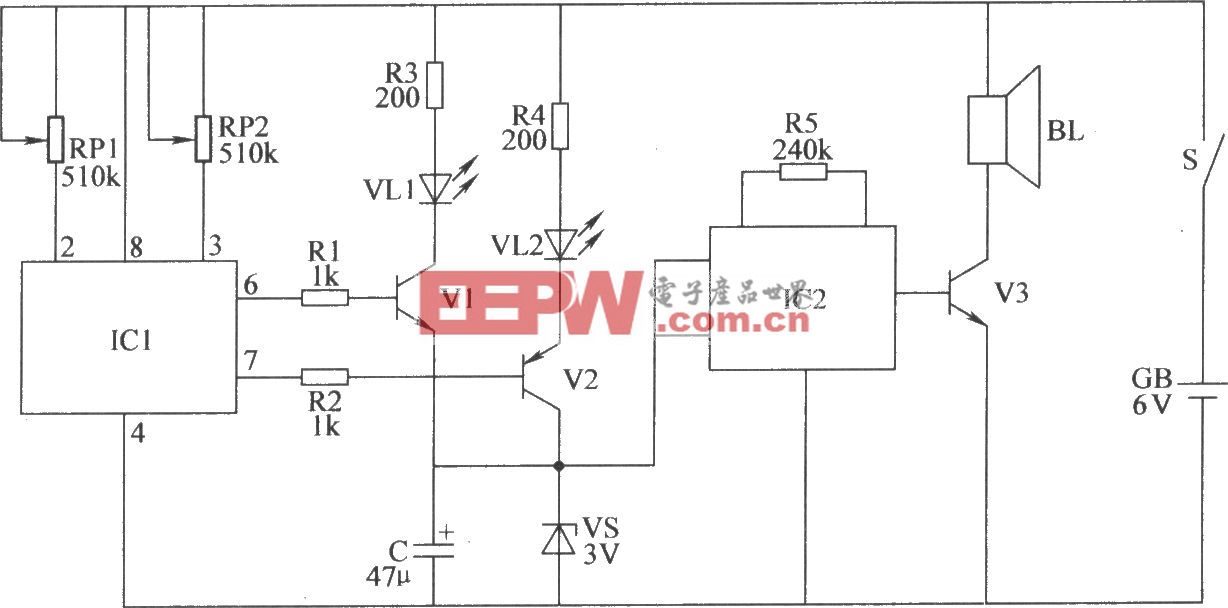

图1给出刷新时钟电路示意图。电路左边是一条反相器反馈链,反相器链输出和使能信号EN共同控制一个两输入端的与非门,与非门的输出连接上拉管MP1的栅极,下拉管MN1栅极和刷新电路的时钟输出;反相器链输入端连接的是电容C1,而且反相器链的输入端的第一个反相器是施密特反相器。电路的右边是时钟调整单元。时钟调整单元主要由一条充放电的通路构成,通路由3个基本的MOS管组成,其中上拉管MP1受与非门输出控制,用于对电容C1进行充电;下拉管MN0也受与非门输出控制,其状态正好与MP1管相反,用于开启放电通路,对电容C1进行放电;放电管MP0主要用于对电容C1放电,以Diodes方式连接。

2 电路工作原理

电路上电后,EN信号使能,电容C1没有储存电荷,Vcap点电压为低电压“0”,通过反相器链的反馈作用,N0点电压是低电压“0”,上拉管MP1开启,下拉管MN1关闭,电源对电容C1充电,MP1的尺寸比较大,所以充电速度比较快,电容C1迅速被充到高电平。当电容C1电压超过了施密特反相器的上翻转点(假设为VM+,VM+>Vdd/2),反相器链开始转变状态,通过反相器链的传播,在N0点处,电压变为高电平“1”,迫使上拉管MP1关闭,下拉管MN1开启,电容C1停止充电,开始通过放电通路泄放电荷,电容电压Vcap开始下降。当电容电压低于施密特反相器的下翻转点(假设为VM-,VM-Vdd/2),反相器状态改变,经过反相器链,N0点电压处重新变为低电平“0”,上拉管MP1开启,下拉管MN1关闭,电容又重新开始充电过程。在反复的充放电过程中,电路在OUT点产生了振荡时钟。

对于MOS电容C1,可以近似认为是平板电容:

C*U=Q

式中:C为电容大小,U为电容电压(即Vcap点电压)。随着放电通路开启,电容C1中的电荷Q逐渐漏失,电容的大小C不变,电容电压U开始下降。同时,对于放电通路,MP0管以DIODES方式连接,MP0一直处于饱和状态,对于饱和电流公式:

![]()

式中:Vth是阈值电压,Vgs是栅源电压。Ugs对应于电路上就是MP0管两端电压,又由于MN1是下拉管,尺寸大,所以放电通路开启后,MP1管的栅端和漏端电压基本等于地电压,而且MP1管的源端又连接在电容上,所以,可以认为Vgs就是电容电压。因为电容电压随着漏电下降,即Vgs随漏电下降。所以根据饱和电流公式,电流Ids呈平方关系减小。随着Ids减小,电容电荷漏失的速度变慢,电容电压下降的速度也随之变慢。

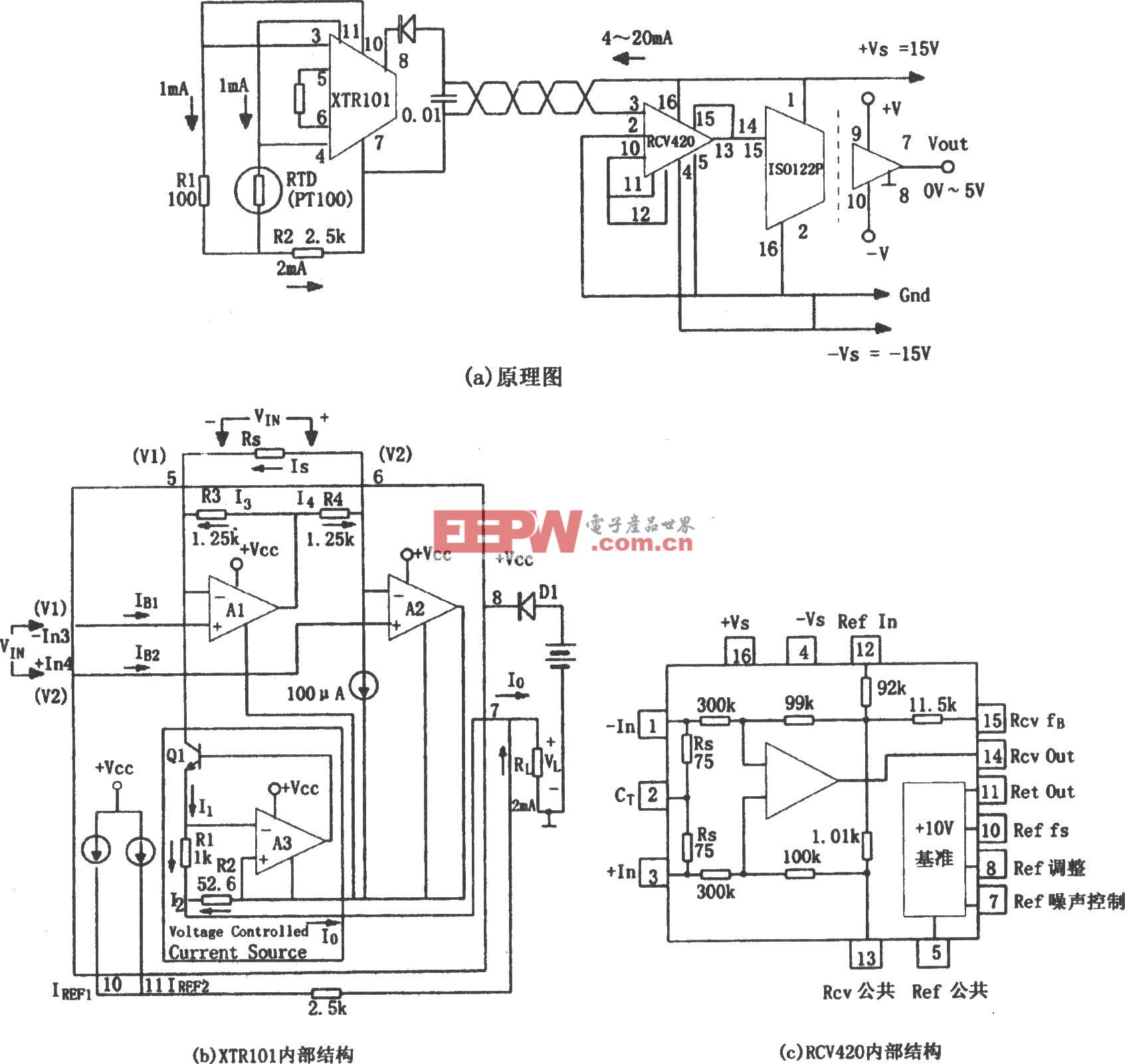

图2说明的是以Diodes方式连接的晶体管,不同温度下的电流和栅源电压之间的关系。当栅源电压比较高的时候,高温时的饱和漏电流比低温时的电流要低;相反地,当栅源电压下降到阈值电压附近,高温时的饱和漏电流就比低温时的电流要高。利用低栅源电压的电流的温度特性,高温时,饱和漏电流Ids比低温时大,电容C1的电压下降得快,更快到达施密特反相器翻转点VM-,电路振荡时钟周期就会比较短,相应地,其频率就更快,就能够体现出时钟温度的特性。

评论