基于层次法实现EOS芯片的后端设计

1 引言

本文引用地址:https://www.eepw.com.cn/article/171655.htm集成电路(Integrated Circuit, IC)是指在一半导体基板上,利用氧化、蚀刻、扩散等方法,将众多电子电路组成各式二极管、晶体管等电子组件,做在一个微小面积上,以完成某一特定逻辑功能,达成预先设定好的电路功能要求的电路系统。

IC设计是将系统、逻辑与性能的设计要求转化为具体的物理版图的过程,也是一个把产品从抽象的过程一步步具体化、直至最终物理实现的过程。

IC设计主要包括两个方面:(A)前端设计 (B)后端设计。前段设计是指设计人员根据系统所要求的功能与时序产生相应的逻辑网表,后端设计是指根据网表产生相应的版图。

后端设计是整个集成电路(IC)设计过程中与产品研制和生产直接相关的设计过程,是集成电路设计的重要组成部分,后端设计的目的是将与工艺无关的通过硬件描述语言(HDL)表示的设计实现成与特定工艺相关的版图。后端设计直接关系到芯片的设计周期、生产成本和产品质量。后端设计以往通常是人工设计中耗时最多,差错率最高的设计过程,也是集成电路设计发展较快,自动化水平较高的领域。在超深亚微米工艺条件下,由于设计复杂度上升和新工艺带来的物理特性变化,后端设计在很多方面需要进行改进以适应新的设计环境。

2 传统的展平的后端设计方法

后端设计的主要流程包括布图规划(floor plan)、电源规划(power plan)、布局(placement)、时钟树综合(clock tree)、布线(routing)、验证仿真到流片[1]。

传统的展平法流程中,首先需要将前端生成的逻辑网表展平,并将设计中的标准单元作为叶节点,不同功能的模块所包含的标准单元都在同一个层次上。在平面设计流程中,各个IP模块是打散(smash)排列的,不需考虑各个模块的功能与位置关系,并利用工具进行自动的布局布线[2]。展平法是将设计一次性的进行综合、布局布线。展平法的优点是流程简单,同时时序性能好,这是因为它能对整个设计进行比较全面的优化。展平法的缺点是设计大小受限于综合和布局布线工具的能力,如果设计规模太大,综合和布局布线可能得不到结果或者结果很差,主要体现在布线布不通或者时序非常难收敛,而且迭代的时间非常长。

3 层次式后端设计方法

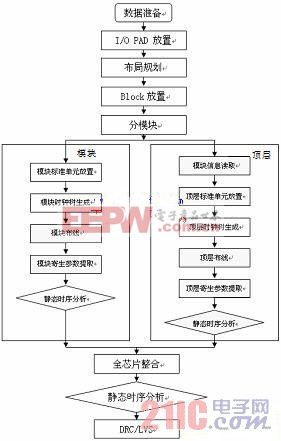

层次法是将设计分成若干个模块,对这些模块分别进行物理实现,然后把这些模块组合成一个完整的设计[3]。图 1显示了层次法设计法的流程。首先,根据逻辑关系将设计分成各个模块,然后将各个模块进行综合,得到各个模块的门级网表(netlist),再将各个模块的门级网表组合成整个芯片的门级网表,将整个芯片的门级网表根据物理关系分成若干个模块,同时通过时序分块(timing budget)得到每个模块的时序要求,根据每个物理模块的门级网表和时序要求,实现每个模块,最后将这些实现的模块集成为一个完整的设计。

图1 层次法后端设计流程

层次法设计包含以下基本步骤:

(1) 数据准备(Data Preparation)

准备好后端设计所需要的数据:网表(netlist),时序约束文件(sdc),单元库(cell library),时序库(tlf)等等。

(2) I/O PAD放置

根据芯片外管脚的定义和模块数据流向手工放置I/O PAD的位置,也可以通过编写TDF(top design format)文件,把PAD 位置进行限制,用自动布局布线工具读入这个文件即可。

(3) 布局规划(Floorplan)

根据设计的数据流向和功能模块的考虑,以及经验值,给出“core utilization”等参数的值的设置,如果之后的布线出现拥塞,可以适当调整这些参数的设置。

(4) 宏单元放置(Marco cell placement)

对模拟模块或者RAM,ROM等宏单元提前放置,一般根据数据流和功能要求放置,如果没有要求可以放置在靠近外围,这样不会影响到标准单元的布线。

(5) 电源(Power)

在PAD连上电源环给I/O供电,芯片内部还要在水平和垂直方向给出多组电源组,这些电源组都会连上沟道(row)的电源,以达到IR DROP的要求。

(6) 标准单元放置(Standard cell placement)

标准单元被放置在预先设置好的沟道(row)里面,这种放置可以时时序驱动的(timing driven),也可以是功耗驱动的(power driven)。

评论