便携产品电源芯片的设计技巧

标签:LDO PCB

本文引用地址:https://www.eepw.com.cn/article/165274.htm随着便携产品日趋小巧轻薄,对电源管理芯片也提出更高的要求,诸如高集成度、高可靠性、低噪声、抗干扰、低功耗等。本文探讨了在便携产品电源设计的实际应用中需要注意的各方面问题。

便携产品的电源设计需要系统级思维,在开发手机、MP3、PDA、PMP、DSC等由电池供电的低功耗产品时,如果电源系统设计不合理,会影响到整个系统的架构、产品的特性组合、元件的选择、软件的设计以及功率分配架构等。同样,在系统设计中,也要从节省电池能量的角度出发多加考虑。例如,现在便携产品的处理器一般都设有几种不同的工作状态,通过一系列不同的节能模式(空闲、睡眠、深度睡眠等)可减少对电池容量的消耗。当用户的系统不需要最大处理能力时,处理器就会进入电源消耗较少的低功耗模式。

从便携式产品电源管理的发展趋势来看,需要考虑以下几个问题:1. 电源设计必须要从成本、性能和产品上市时间等整个系统设计来考虑;2. 便携产品日趋小巧轻薄化,必需考虑电源系统体积小、重量轻的问题;3. 选用电源管理芯片力求高集成度、高可靠性、低噪声、抗干扰、低功耗,突破散热瓶颈,延长电池寿命;4. 选用具有新技术的新型电源芯片进行方案设计,这是保证产品先进性的基本条件,也是便携产品电源管理的永恒追求。

便携产品常用电源管理芯片包括:低压差稳压器(LDO)、非常低压差稳压器(VLDO)、基于电感器储能的DC/DC转换器(降压电路Buck、升压电路Boost、降压-升压变换器Buck-Boost)、基于电容器储能的电荷泵、电池充电管理芯片、锂电池保护IC。

选用电源管理芯片时应注意:选用生产工艺成熟、品质优秀的生产厂家产品;选用工作频率高的芯片,以降低周边电路的应用成本;选用封装小的芯片,以满足便携产品对体积的要求;选用技术支持好的生产厂家,方便解决应用设计中的问题;选用产品资料齐全、样品和DEMO易于申请、能大量供货的芯片;选用性价比好的芯片。

LDO线性低压差稳压器是最简单的线性稳压器,由于其本身存在DC无开关电压转换,所以它只能把输入电压降为更低的电压。它最大的缺点是在热量管理方面,因为其转换效率近似等于输出电压除以输入电压的值。

LDO电流主通道在其内部是由一个MOSFET加一个过流检测电阻组成,肖特基二极管作反相保护,输出端的分压电阻取出返馈电去控制MOSFET的流通电流大小,EN使能端可从外部去控制它的工作状态,内部还设置过流保护、过温保护、信号放大、Power-OK、基准源等电路,实际上LDO已是一多电路集成的SoC。LDO的ESD>4KV,HBM ESD>8KV。

低压差稳压器的应用象三端稳压一样简单方便,一般在输入、输出端各加一个滤波电容器即可。电容器的材质对滤波效果有明显影响,一定要选用低ESR的X7R X5R陶瓷电容器。

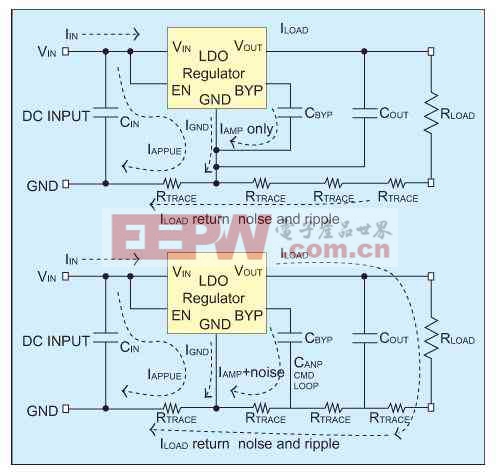

LDO布线设计要点是考虑如何降低PCB板上的噪音和纹波,如何走好线是一个技巧加经验的工艺性细活,也是设计产品成功的关键之一。图1说明了如何设计走线电路图,掌握好电流回流的节点,有效的控制和降低噪音和纹波。优化布线方案是值得参考的。

图1:LDO布线电路方案

如果一个驱动图像处理器的LDO输入电源是从单节锂电池标称的3.6V,在电流为200mA时输出1.8V电压,那么转换效率仅为50%,因此在手机中产生一些发热点,并缩短了电池工作时间。虽然就较大的输入与输出电压差而言,确实存在这些缺点,但是当电压差较小时,情况就不同了。例如,如果电压从1.5V降至1.2V,效率就变成了80%。

当采用1.5V主电源并需要降压至1.2V为DSP内核供电时,开关稳压器就没有明显的优势了。实际上,开关稳压器不能用来将1.5V电压降至1.2V,因为无法完全提升MOSFET(无论是在片内还是在片外)。LDO稳压器也无法完成这个任务,因为其压差通常高于300mV。

理想的解决方案是采用一个VLDO稳压器,输入电压范围接近1V,其压差低于300mV,内部基准接近0.5V。这样的VLDO稳压器可以很容易地将电压从1.5V降至1.2V,转换效率为80%。因为在这一电压上的功率级通常为100mA左右,那么30mW的功率损耗是可以接受的。VLDO的输出纹波可低于1mVP-P。将VLDO作为一个降压型开关稳压器的后稳压器就可容易地确保低纹波。

开关式DC/DC升降压稳压器

开关式DC/DC升降压稳压器按其功能分成Buck开关式DC/DC降压稳压器、Boost开关式DC/DC升压稳压器和根据锂电池的电压从4.2V降低到2.5V能自动切换降升压功能的Buck-Boost开关式DC/DC升降压稳压器。当输入与输出的电压差较高时,开关稳压器避开了所有线性稳压器的效率问题。它通过使用低电阻开关和磁存储单元实现了高达96%的效率,因此极大地降低了转换过程中的功率损失。

Buck开关式DC/DC降压稳压器是一种采用恒定频率、电流模式降压架构,内置主(P沟道MOSFET)和同步(N沟道MOSFET)开关。PWM控制的振荡器频率决定了它的工作效率和使用成本。选用开关频率高的DC/DC可以极大地缩小外部电感器和电容器的尺寸和容量,如超过2MHz的高开关频率。开关稳压器的缺点较小,通常可以用好的设计技术来克服。但是电感器的频率外泄干扰较难避免,设计应用时对其EMI辐射需要考虑。

图2给出了Buck开关式DC/DC应用线路设计,需要注图中粗线的部分:粗线是大电流的通道;选用MuRata、Tayo-Yuden、TDKAVX品质优良、低ESR的X7R X5R陶瓷电容器;在应用环境温度高,或低供电电压和高占空比条件下(如降压)工作,要考虑器件的降温和散热。必须注意:SW vs. L1距离4mm;Cout vs. L1距离4mm;SW、Vin、Vout、GND的线必须粗短。

要得到一个运作稳定和低噪音的高频开关稳压器,需要小心安排PCB板的布局结构,所有的器件必需靠近DC/DC,可以把PCB板按功能分成几块,如图3所示。1. 保持通路在Vin、Vout之间,Cin、Cout接地很短,以降低噪音和干扰;2. R1、R2和CF的反馈成份必须保持靠近VFB反馈脚,以防噪音;3. 大面积地直接联接2脚和Cin、Cout的负端。

评论