一种基于FPGA的DDR SDRAM控制器的设计

2 DDR SDRAM控制器的设计

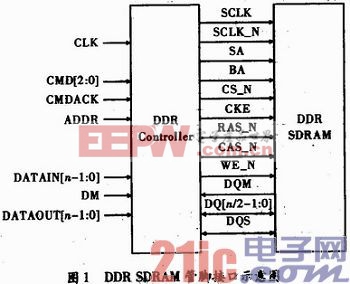

为能像操作普通存储器—样对DDR SDRAM进行控制,必须要通过一系列的初始化操作完成对DDRSDRAM复杂的读写时序转换。同时DDR SD RAM控制器还要自行产生周期性的Auto Refresh命令自动刷新DDR SDRAM,以保证存储数据的稳定性。图1为DDR SDRAM控制器管脚接口示意图,控制器右端的管脚接口与DDR SDRAM所对应管脚接口直接相连,控制器左端的管脚接口则是接收来自系统发送的控制信号。本文引用地址:https://www.eepw.com.cn/article/159415.htm

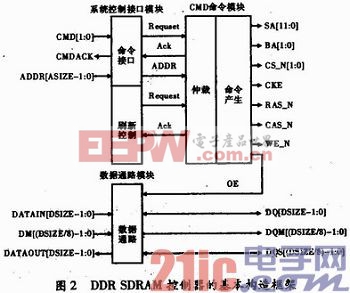

DDR SDRAM控制器的基本构造框架如图2所示:分别是系统控制接口模块ddr_control_interface、CMD命令模块ddr_command和数据通路模块ddr_data_path。ddr_control_interface包括命令接口模块和刷新控制模块,系统发出的控制信号会首先进入ddr_control_interface,进而产生不同的commsnd信号组合;ddr_command用于接收系统控制接口模块产生的command,并解码成具体的操作命令对DDR SDRAM进行控制;ddr_data—path主要是对输入和输出数据进行有效的控制。

2.1 系统控制接口模块

图3为系统控制接口模块ddr_control_interface的有限状态机。控制器接收到后模块发送的LOAD_REG1命令后进入载入模式,然后由一个LOAD_REG2命令将刷新计数器值载入控制器。控制器发送Read/Write操作请求时,如果DDR SDRAM正处于IdleState,则需要使用Active命令打开相应的行之后才能进入Read/Write状态。DDR SDRAM的Read/Write访问是基于突发方式,有2、4、8这3种突发长度。在突发长度为8的状态下,DDR SDRAM接收Read命令后会在指定的延迟后的4个时钟周期内,由DQ数据线给出8个16位数据,完成1次突发Read操作。执行完1次突发Read操作,控制器便会自动转入Read等待状态,这个等待状态将持续到控制器接收到下一个Read命令。如果此时发送1个Precharge命令关闭当前正在工作的行,控制器就会进入Idle State。连续突发Bead操作可以通过设置Read等待状态来实现而不必重复Active操作。当Read操作发生在不同的行时,需要先使用Precharge命令关闭正在工作的行,再由Active打开需要读取的另一个行,而此时的访问耗时最长。

电容器相关文章:电容器原理

fpga相关文章:fpga是什么

电荷放大器相关文章:电荷放大器原理 漏电开关相关文章:漏电开关原理 锁相环相关文章:锁相环原理

评论