一种基于FPGA的DDR SDRAM控制器的设计

2.2 CMD命令模块

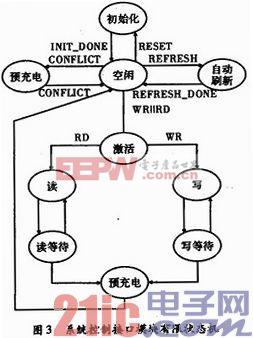

CMD命令模块ddr_command由仲裁模块以及命令产生模块构成。仲裁模块的作用主要是仲裁初始化请求、刷新请求以及读写请求的优先级,并产生初始化响应initial hold、刷新响应refresh hold和读写响应sdram wr hold。命令产生模块则是实现存储器与控制之间的命令通信,直接产生存储器所需的CKE、CS_N,RAS_N,CAS_N,WE_N等命令信号。除此之外Read/Write所需的行列地址和簇地址也由命令模块产生。命令产生模块接收到来自CMD命令解析模块的操作命令后,根据数据选通倍号OE对数据通路模块进行有效控制:OE为1时,进行Write操作;OE为0时,进行Read操作。

2.3 数据通路模块

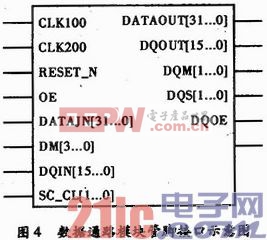

数据通路模块ddr_data_path受命令产生模块的OE信号控制,其管脚接口如图4所示。OE为1时,数据可由DQIN引脚写入DDR SDRAM;OE为0时,数据可从DDR SDRAM的DQIN引脚读出。

由于DDR SDRAM在时钟的上升沿和下降沿能均触发数据,使得用户端的数据宽度是DDR SDRAM的两倍。进行Read操作时,DQ pins上的双倍速率数据经过边沿触发器,在DQS信号的两个边沿同时采样数据,然后这些数据会通过另一套可配置的寄存器被传送到系统的时钟域。进行Write操作时,用户端寄存器输出的数据会被传送到控制器的寄存器中,进而被存放到DQ pins上。数据通路模块在与存储器的接口处完成了两个转换:一是翻倍来自存储器的数据总线宽度;二是以400 MHz的时钟频率接收存储器在时钟上升和下降沿发出的数据。

电容器相关文章:电容器原理

fpga相关文章:fpga是什么

电荷放大器相关文章:电荷放大器原理 漏电开关相关文章:漏电开关原理 锁相环相关文章:锁相环原理

评论