一种基于FPGA的DDR SDRAM控制器的设计

摘要 对DDR SDRAM的基本工作特性以及时序进行了分析与研究,基于FPGA提出了一种通用的DDRSDRAM控制器设计方案。在Modelaim上通过了软件功能仿真,并在FPGA芯片上完成了硬件验证。结果表明,该控制器能够较好地完成DDR SDRAM的读写控制,具有读写效率较高、接口电路简单的特点。

关键词 DDR SDRAM;控制器;FPGA

随着超大规模集成电路技术的成熟,以及数字信号处理技术的广泛应用,高速大容量缓存逐渐成为一项关键技术。DDR SDRAM即双倍速率同步动态随机存储器,它采用地址复用技术,在时钟的上升沿和下降沿均能触发数据进行传输,并且能与系统保持良好的同步性。DDR SDRAM以其大容量、低成本以及更高的数据传输质量等优势,逐步取代SDRAM而被各集成电路制造厂家所青睐。而要实现各微处理器和数字信号处理器的存储器接口与DDR SDRAM接口相逢接,必须要借助DDR SDRAM控制器才能实现控制读写等功能。微电子制造工艺的迅猛发展使得FPGA的集成度和性能也不断提高,在各种嵌入式系统中的应用也越来越广泛。FPGA内部集成了DDR触发器、PLL锁相环等逻辑资源,并且其引脚均能满足SSTL-Ⅱ电器特性的要求,因此FPGA是实现DDR,读写控制的最佳平台,研究如何利用FPGA实现DDR SDRAM控制器具有重要的现实意义。

1 DDR SDRAM的工作特性

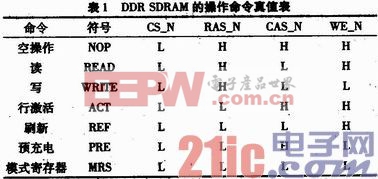

一个DDR SDRAM通常包含有地址总线15个、数据总线16个、数据捕获探针2个、写掩码信号线2个、差分主控时钟线1个、时钟使能信号线1个、以及命令信号线4个:CS_N,RAS_N,CAS_N,WE_N。

1.1 DDR SDRAM的初始化

DDR SDRAM的工作模式必须由初始化操作来配置,初始化的过程通常包含:首先发送一个Prechargeall bank命令完成对所有块的预充,接下来是两个或多个Auto Refresh命令使DDR SDRAM进行自动刷新,最后由模式配置命令完成对DDR SDRAM内部模式设置寄存器的配置。

1.2 访问存储单元

为减少输入输出引脚的数量,初始化完成后要对各个Bank中的阵列进行寻址以访问存储单元:在Read/Write状态下先由Active命令激活相关的Bank,并锁存其行地址,当Read/Write命令有效时锁存列地址。对于已被激活由同一个Bank,再次激活必须重新执行一次Prechar ge all bank命令。

1.3 刷新

DDR SDRAM的存储单元由晶体管和电容器组成,电容器会由于漏电而导致电荷丢失,为保证数据存储的稳定性,必须周期性地对DDR SD RAM进行刷新。控制器内部的自动刷新计数器每隔一个刷新周期便会发送一个刷新请求,控制器在接收到请求后会根据当前DDR SDRAM的状态做出不同响应:如果此时DDRSDRAM处于Idle State,控制器便会发出一个AutoRefresh命令对DDR SDRAM进行刷新;如果此时DDR SDRAM正在进行Read/Write操作,控制器会等到当前操作完成之后再发送Auto Refresh命令。

1.4 操作控制

DDR SDRAM的操作命令由专用的命令控制信号决定。具体会执行何种操作动作决定于系统时钟上升沿时的CS_N(片选信号),RAS_N(行地址使能信号),CAS_N(列地址使能信号)以及WE_N(写使能信号)的状态。DDR SDRAM操作命令真值表如表1所示,选择控制信号线和地址信号线只作为辅助参数输入。

电容器相关文章:电容器原理

fpga相关文章:fpga是什么

电荷放大器相关文章:电荷放大器原理 漏电开关相关文章:漏电开关原理 锁相环相关文章:锁相环原理

评论