一种基于FPGA的DDR SDRAM控制器的设计

3 DDR SDRAM控制的仿真和验证

3.1 DDR SDPAM控制器的软件仿真

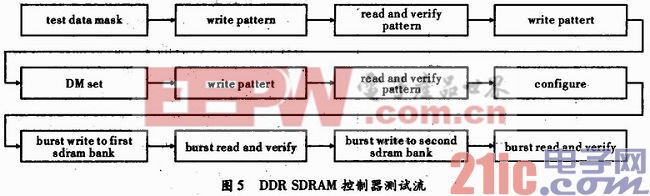

设计的软件功能仿真是利用硬件描述语言VerilogHDL写出测试代码,在Mentor公司的Modelsim软件中进行,通过检查波形完成。DDR SD RAM控制器测试流如图5所示,实现了写数据到第1组寄存器,读校验数据,写数据到第2组寄存器,读校验数据。本文引用地址:http://www.eepw.com.cn/article/159415.htm

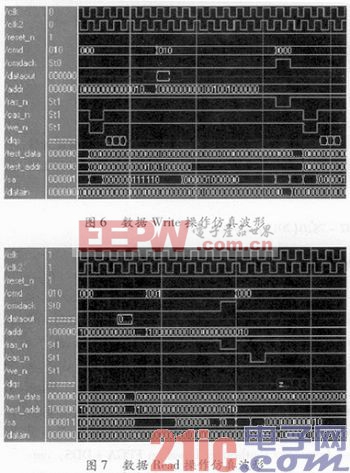

当控制器接收到请求发送数据的命令后,由命令引脚产生相应的Write命令传送给DDR SDRAM,接下来会反馈—个握手信号ready以告知用户端已准备就绪可以继续接收数据,而接收到的数据通过dq端口直接传给DDR SDRAK。经过Modelsim功能仿真Read/Write波形如图6和图7所示,结果表明DDR SDRAM能顺利地完成读写、刷新和预充电,行与行、块与块之间的交换平稳迅速,无论是连续还是单个操作都非常顺畅。

3.2 DDR SDRAM控制器的FPGA验证

设计的DDR SDRAM控制器硬件验证在Altera公司CycloneII系列的EP2C5Q208C8 FPGA芯片中进行,利用在线仿真技术快速建立芯片设计的硬件模型,然后将设计映射至目标FPGA电路中,通过加载设定的激励信号,观察所输出的结果并与所期望的输出结果进行比较,发现写入和输出的数据完全吻合。经过综合,基础逻辑单元资源占用率为12.33%,引脚资源占用率为62.5%,锁相环PLL资源的占有率为50%,流片频率测试也能达到期望要求,能完全胜任对DDRSDRAM控制。

4 结束语

在研究DDR SDRAM的主要工作特性以及时序的基础上,利用Verilog HDL硬件描述语言提出了一种适用于DDR SDRAM的控制器的设计。并且通过了Modelsim软件功能仿真、FPGA硬件验证,结果表明该设计传输数据稳定可靠,读写效率较高,接口电路简单,可应用于各种高速度、大容量存储器场合中。

电容器相关文章:电容器原理

fpga相关文章:fpga是什么

电荷放大器相关文章:电荷放大器原理 漏电开关相关文章:漏电开关原理 锁相环相关文章:锁相环原理

评论