14nm是全球半导体工艺的一个“坎”?

尺寸缩小是推动产业进步的“灵舟妙药”,每两年尺寸缩小70%的魔咒至此没有延缓的迹象,2011年是22nm工艺,到2013年工艺应该到14nm。众所周知,尺寸缩小仅是一种手段,如果缺乏尺寸缩小而带来的红利,业界不会盲目跟进。依目前的态势,业界已然有所争议,有人认为由28nm向22nm过渡时成本可能反而上升,这或是产业过渡过程中的正常现象。

本文引用地址:https://www.eepw.com.cn/article/159122.htm全球半导体业中还能继续跟踪14nm工艺节点者可能尚余不到10家,包括英特尔、三星、台积电、格罗方得、联电、东芝、海力士、美光等。显然在半导体业中领军尺寸缩小的企业是NAND闪存及CPU制造商及一批FPGA厂商。而如台积电等代工制造商,由于从市场需求出发,通常工艺制程会落后一代。由此也并非表示代工模式一定会落后于IDM,因为市场经济是需要权衡技术能力与成本的。近期也出现如FPGA的Altera跳过台积电而直接寻求与英特尔合作开发14nmFPGA,反映市场的错踪复杂。

众所周知,尺寸缩小仅是一种手段,如何继续往下走,似乎业界把希望押宝在FinFET3D工艺与EUV光刻上。从长远来看,集成电路产业的发展总是在性能、成本和功耗三者之间做平衡,由市场做出最后的选择。应在保持性能的前提下,尽可能地降低成本,同时在保持性能与成本的前提下应该尽可能地降低功耗。

市场调研机构Gartner的分析师DeanFreeman日前表示,目前半导体业界所面临的情况与上世纪80年代的情形非常相似,当时业界为了摆脱面临的发展瓶颈,开始逐步采用CMOS技术来制造内存和逻辑芯片,从而开创了半导体业界的新纪元。而目前采用FinFET的3D工艺会否产生同样的光环,业界值得期待。

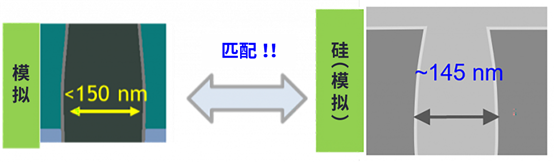

14nm纳米是个壁垒或者“坎”。尽管英特尔至今并没有疑虑,仍坚挺采用193nm浸液式光刻加上两次图形曝光等辅助技术,将于2013年底时会推出14nm的测试芯片,并于2014年开始量产。然而在业界似乎已产生分歧,如台积电从20nm之后的下一个工艺节点设定为16nm。

对于22nm/16nm级别的工艺制程,业界认为有多种晶体管结构可供选择,包括III-V族沟道技术、体硅技术、FinFET立体晶体管技术、FD-SOI全耗尽型平面晶体管技术以及多栅立体晶体管技术等。但是依目前的分析来看,自14nm(包括14nm)之后,采用FinFET3D结构工艺或将成为主流技术。

在现阶段尚有两种技术在互相争艳:一种是如英特尔表示会在22nm制程中开始采用FinFET结构的三栅晶体管技术。另一种是如IBM、意法半导体等公司表示考虑在22nm制程节点时采用FD-SOI或者FD-UTSOI全耗尽技术。IBM公司曾经在前两年展示了一种基于超薄的FD-UTSOI工艺。此种工艺技术的优点是仍然基于传统的平面型晶体管结构,不过这种工艺的SOI的硅层厚度非常薄,在5nm~6nm之间,这样便于形成全耗尽(FD)结构,能够显著减小短沟道效应(SCE)的影响。

尽管英特尔与IBM双方采用的工艺技术路线不尽相同,然而市场经济是公平的,双方都会各展所长,根据市场需求做出权衡。

晶体管相关文章:晶体管工作原理

晶体管相关文章:晶体管原理

评论