嵌入式系统中Nand-Flash的原理及应用

Nand-flash存储器是flash存储器的-种,其内部采用非线性宏单元模式,为固态大容量存储器的实现提供了廉价有效的解决方案。Nand-flash存储器具有容量较大,改写速度快,适用于大量资料的存储,因而在业界得到了越来越广泛的应用,如嵌入式产品中包括数码相机、MP3随身听记忆卡、体积小巧的U盘等。

本文以三星公司的K9F1208UOB芯片为例,介绍Nand-flash存储器芯片的读写流程和时序。

1 Nand-Flash存储器的工作原理

1.1 Nand-Flash存储器的组成结构及指令集

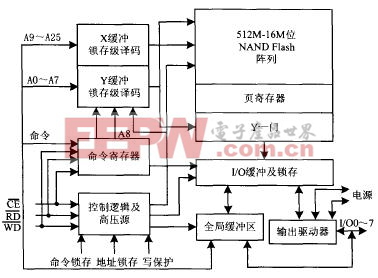

K9F1208UOB的容量为64Mb,存储空间按128K个页(行)、每页中528个字节(列)的组成方式构成。备用的16列,位于列地址的512-527。K9F1208UOB还将存储空间分为块(block),每1块由32个页构成。因此K9F1208UOB中一共有4096个块。这种“块-页”结构,恰好能满足文件系统中划分簇和扇区的结构要求。K9F1208UOB的内部结构如图1所示。

图1 K9F1208UOB的内部结构

K9F1208UOB的读和写都以页为单位,擦除则以块为单位进行操作。

K9F1208UOB的地址通过8位端口传送,有效地节省了引脚的数量,并能够保持不同密度器件引脚的一致性,系统可以在电路不作改动的情况下升级为高容量存储器件。

K9F1208UOB通过CLE和ALE信号线实现I/O口上指令和地址的复用。指令、地址和数据都通过拉低WE和CE从I/O口写入器件中。有一些指令只需要一个总线周期完成,例如,复位指令、读指令和状态读指令等;另外一些指令,例如页写入和块擦除,则需要2个周期,其中一个周期用来启动,而另一个周期用来执行。

1.2 Nand-Flash操作

1.2.1 页读操作

在初始上电时,器件进入缺省的“读方式1模式”。在这一模式下,页读操作通过将00h指令写入指令寄存器,接着写入3个地址(1个列地址,2个行地址)来启动。一旦页读指令被器件锁存,下面的页读操作就不需要再重复写入指令了。

写入指令和地址后,处理器可以通过对信号线R/B的分析来判断该操作是否完成。如果信号为低电平,表示器件正“忙”;为高电平,说明器件内部操作完成,要读取的数据被送入了数据寄存器。外部控制器可以在以50ns为周期的连续RE脉冲信号的控制下,从I/O口依次读出数据。连续页读操作中,输出的数据是从指定的列地址开始,直到该页的最后-个列地址的数据为止。

1.2.2 页写操作

K9F1208UOB的写入操作也以页为单位。写入必须在擦除之后,否则写入将出错。

页写入周期总共包括3个步骤:写入串行数据输入指令(80h),然后写入3个字节的地址信息,最后串行写入数据。串行写入的数据最多为528字节,它们首先被写入器件内的页寄存器,接着器件进入一个内部写入过程,将数据从页寄存器写入存储宏单元。

评论