自适应时钟技术在芯片设计与验证中的应用

0 引言

本文引用地址:https://www.eepw.com.cn/article/149660.htm随着半导体工艺的迅速发展,嵌入式处理器和DSP的设计越来越复杂,其开发调试工作也日趋重要,因此处理器平台提供强大的调试系统已成为设计中必不可少的一部分。

嵌入式处理器调试系统使用硬件仿真器将调试软件与目标芯片接连起来。仿真器与PC机之间通过标准的计算机通信接口(以太网、USB、串口等)进行通信;仿真器与目标芯片之间通过符合IEEEll49.1标准的JTAG(Joint Test AcTIon Group)信号进行数据传输。随着处理器和仿真器主频的不断提升,传统的JTAG接口设计以其缺乏对JTAG信号传输进行必要的时序匹配,而无法确保仿真器和目标芯片对JTAG信号进行稳定可靠的接收,因此不能满足高性能嵌入式系统的要求。

在此,提出一种双向同步自适应时钟技术,在仿真器与目标处理器之间稳定可靠地实现了跨时钟域JTAG信号的双向时序匹配,并在此基础上设计了一种TCK时钟信号产生算法,从而解决了调试系统软/硬件协同验证中JTAG信号交互时的时序匹配问题。

1.1 基本概念

自适应时钟(Adaptive Clocking)是一种信号同步技术,其基本原理来源于异步电路设计中的自动调时(SelfTimed)技术,即采用类似应答机制来实现两个不同时钟域系统间信号的可靠传输,如图l所示。

图l中的发送与接收系统均工作在各自独立的时钟域下,并对异步输入信号进行采样同步。发送系统(Transmit System)以时钟clk_t为基准,向接收系统(Receive SySTem)发送数据data_t。接收系统将信号clk_t采样同步后产生clk_r,并作为应答信号反馈给发送系统,发送系统接收到clk_r信号,就认为接收系统已经完成了数据接收或处理,可以继续发送新的时钟和数据。此外,如果接收系统也需要向发送系统传送数据data_r,则以clk_r为基准,便于发送系统采用同样的机制接收。

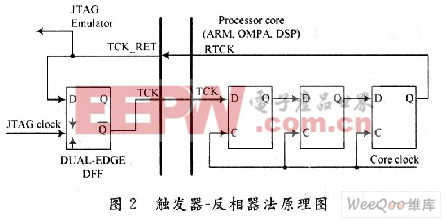

自适应时钟机制通常采用多级同步器实现,一般由几个D触发器构成,如图2所示。同步器将时钟信号TCK同步到内核时钟域。同步器的级数Ns通常与具体的器件相关,一般取值为3或者4。TCK_RET来自最后一级D触发器的输出,作为TCK的“应答”信号,反馈给调试系统。

TCK信号频率的理论最大值可以根据内核时钟频率和Ns的值,由下式简单计算得到:

自适应时钟协议是一种通过目标系统来控制TCK速率的机制,这种机制的优点在于它能够把所有的信号传输延迟(包括JTAG电缆引入的延时)都考虑在内,从而避免了由于传输延迟带来的接收数据损坏,有效提高系统性能。

自适应时钟的另一个优点是可以使仿真器工作在最优的TCK时钟频率下。如果仿真器支持可变的TCK频率,但没有使用自适应时钟技术,用户就必须通过实验来设置TCK的最高工作频率和稳定工作频率。

自适应时钟的第三个优点是如果芯片内核时钟也是可变的,那么TCK_RET信号也会在工作时随之变化,从而保证传输数据能够随时被仿真器正确同步并采样。

1.2 研究背景

目前自适应时钟技术主要用于嵌入式处理器芯片的在线仿真器(In-Circuit Emulator,ICE),简称仿真器。仿真器可以为开发人员提供嵌入式处理器的实时调试和性能微调功能,该系统通过符合IEEE1149.1标准的JTAG接口与芯片内部逻辑进行数据交换。

ARM公司最先在其嵌入式处理器的仿真器EmbeddedICE-RT中采用了自适应时钟技术。最近,TI公司也在其0MAP系列嵌入式处理器的仿真器Blackhawk JTAG Emulator中采用了自适应时钟技术。它们的自适应时钟都基于触发器-反相器法,如图2所示。在采样TCK_RET信号时,使用一个双边沿D触发器(D-type Flip-Flop,DFF),这样可以避免最终产生的TCK时频率被降低一半。

触发器-反向器法自适应时钟技术仅对TCK信号进行同步,并没有对TCK_RET信号同步,因此TCK信号容易产生不定态输出,从而导致整个系统失效。此外,TCK信号的产生模式没法由仿真器控制,因而灵活性差,适用范围窄,并且在没有JTAG信号传输时TCK信号无法关断,这不仅增加了系统功耗,而且也增加了板级JTAG信号间的干扰。

笔者参与了国内一款高性能DSP芯片的研发工作,同时还负责该芯片的调试系统设计,基于自适应时钟的基本原理,提出了双向同步自适应时钟技术。该时钟技术具有如下优点:

(1)对TCK和TCK_RET分别进行同步,确保JTAG信号双向通信的可靠性和稳定性;

(2)TCK信号由硬件算法产生,可以根据应用需要灵活调整信号特征,从而解决了芯片设计中软/硬件协同验证的时序匹配问题;

(3)在没有JTAG通信的间隙能够主动关闭TCK信号,降低系统功耗,减小板级的信号干扰;

(4)由于仿真器时钟域和处理器时钟域之间的异步关系,产生TCK时钟信号时会引入抖动(Jitter)。该抖动对系统是有益的,它会对TCK信号引入扩频调节,从而降低电磁干扰(Electro Magnetic Interference,EMl),提高系统的电磁兼容性(Electro Magnetic Compatibmty,EMC)。

2 双向同步自适应时钟技术

随着嵌入式处理器性能的增强,仿真器需要处理的在线调试功能也随之增强,因此仿真器本身也需要工作在比较高的时钟频率下,从而能够在有限的时间内处理足够多的调试信息。通常使用JTAG时钟信号TCK的频率相对比较低,在1~20 MHz之间,已经远远无法满足仿真器的工作需要。双向同步自适应时钟机制能够保证仿真器和处理器都工作在各自的高频时钟下,同时还能够实现可靠的JTAG信号传输。

2.1 原理

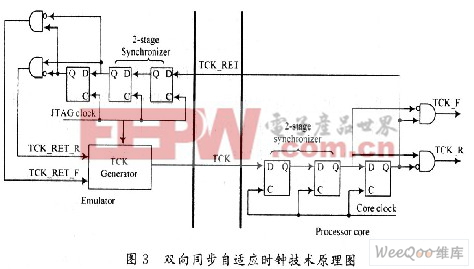

双向自适应时钟技术的原理如图3所示。

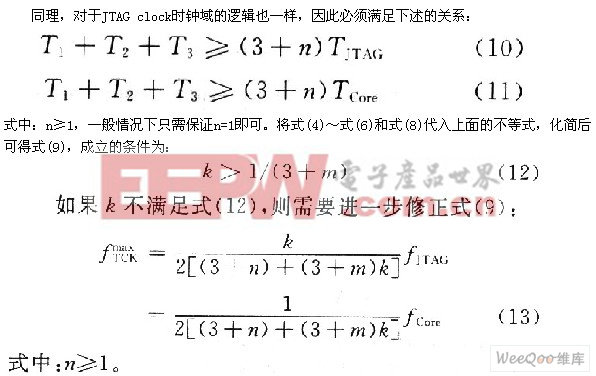

仿真器工作在JTAG clock时钟域,其频率为fJTAG;所有由仿真器发送给处理器内核的JTAG信号都由该时钟域的逻辑产生,并与TCK对齐,TCK的频率为fTCK。处理器内核工作在Core clock时钟域,其频率为fCore;JTAG clock,TCK和Core clock这三组时钟信号之间通常满足下述基本关系:

由于TCK和TCK_RET信号在两个异步时钟域之间传输,为了消除跨时钟域信号传输可能带来的不定态导致系统失效,处理器内核和仿真器都需要分别对这两个信号进行同步和采样,即双向同步。同步器采用2级D触发器级联构成,这种结构可以保证系统在108s(大约3年)内失效的次数少于1次,从而解决绝大部分跨时钟域信号的不定态问题。如果在特殊情况下需要进一步提高系统的稳定性,可以继续增加D触发器的级联数目,但是这样做会增加系统的延迟,因此需要在性能和稳定性之间进行权衡。

TCK信号经过Core clock时钟同步之后产生TCK_RET信号,反馈给仿真器,从而实现自适应时钟技术。同时,由处理器内核向仿真器发送的JTAG信号(例如TDO)与TCK_RET信号对齐。TCK_R和TCK_F可作为Core clock时钟域的门控信号,分别在TCK的上升沿或者下降沿使能处理器内核对JTAG信号进行采样或处理。

TCK_RET信号被JTAG clock时钟同步。TCK_RET_R表示采样到TCK_RET的上升沿,TCK_RET_F表示采样到TCK_RET的下降沿。这两个信号送给TCK时钟产生逻辑,用来根据当前TCKRET信号的接收情况产生下一个TCK信号及相关的JTAG控制和数据信号。

2.2 性能分析

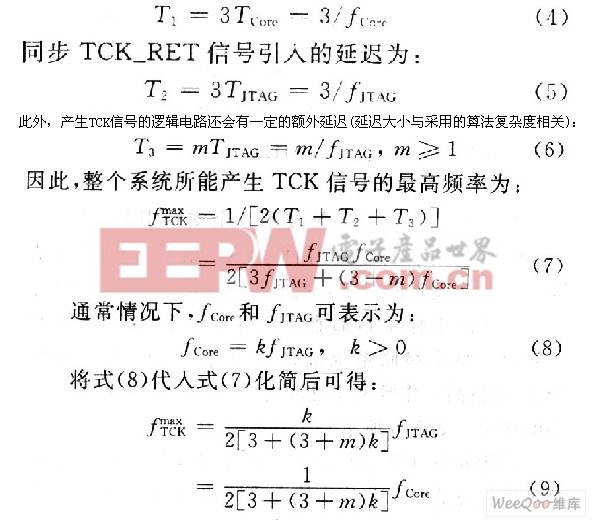

双向同步技术引入了两个同步器,分别用来确保TCK和TCK_RET信号能够被异步时钟正确采样,因此各自增加了一定的系统延迟。同步TCK信号引入的延迟为:

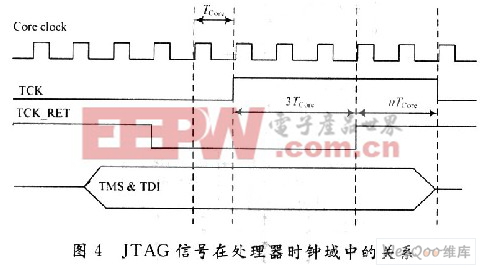

要保证图3中Core clock时钟域逻辑电路能够在TCK_RET信号上升沿采样到稳定的数据,JTAG信号必须满足图4中的关系。

在DSP设计中,fCore=500 MHz,fJTAG=100 MHz,并假设m=1,代入式(9)计算可得TCK信号的最高频率大约为10.9 MHz。

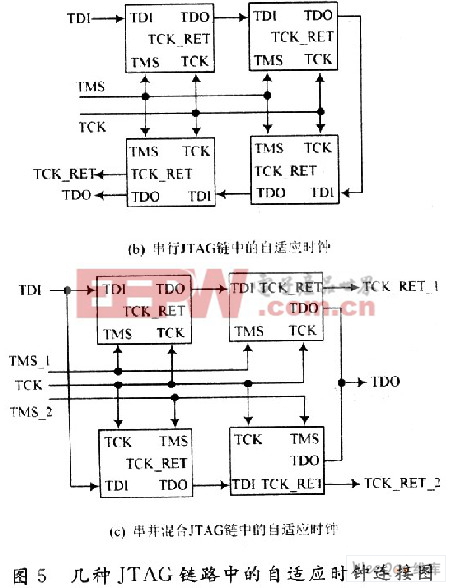

2.3 多芯片级联结构

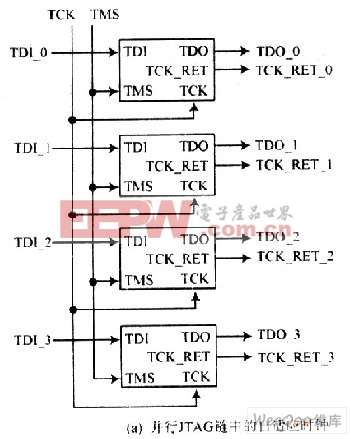

双向同步自适应时钟技术完全支持IEEEll49.1协议中定义的各种多芯片间JTAG信号板级互联结构。多芯片级联情况下,通过式(9)或式(13),根据每一块芯片的工作主频都能计算得到一个对应的TCK频率值。整个级联系统最终使用的JTAG时钟信号TCK的最高工作频率不能超过所有TCK频率值中最小的那个。如图5所示。

采用并行互联结构的JTAG链路,多芯片自适应时钟连接方式与单芯片连接方式一致,每块芯片都提供一路被自身时钟域所同步的自适应时钟TCK_RET,如图5(a)所示。

对于采用串行菊花链结构的JTAG链路,自适应时钟TCK_RET仅来自于链路上最接近TDO输出端一侧的那块芯片,其他芯片不提供自适应时钟,如图5(b)所示。

对于串/并混合连接的多芯片JTAG链路,自适应时钟的连接是上述两种连接方式的混合,如图5(c)所示。

多芯片系统的JTAG连接方式一般都采用串行菊花链结构,从而确保其JTAG链路与仿真器接口与单芯片情况下一致,并能够简化系统设计。

随着嵌入式处理器设计的规模越来越大,复杂度越来越高,功能验证已经成为设计过程中的首要瓶颈。为了提高验证速度,通常采用专门的硬件加速器,笔者参与的高性能DSP设计项目采用了Cadence公司XtremeⅢ硬件加速器,以加速设计功能的验证。XtremeⅢ是基于FPGA的硬件模拟器,它是专门为运行模拟(Simulation)而特别设计的计算机。硬件模拟器只能验证逻辑功能,而不能验证时序性质,因为来自FPGA网络或者处理器的时延与系统设计过程中的时延无关。使用硬件模拟器时,主要瓶颈是硬件模拟器与主机之间的交互(又称系统调用)。因此,在软/硬件协同验证中。真实的硬件系统在与基于硬件模拟器的系统发生信号交互时,时序匹配成为最大的难题。

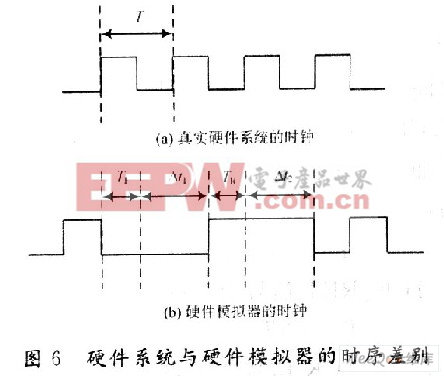

图6说明了硬件模拟器的时钟与真实硬件系统时钟间的差别。真实硬件系统产生的是绝对时钟信号,它的周期是一个固定值T,如图6(a)所示。硬件模拟器与软件模拟器类似,只有相对时钟概念。它在被模拟系统的时钟上升沿和下降沿处分别计算系统中所有的事件,如图6(b)所示。对于特定的设计,无系统调用时,虚拟时钟信号周期Ts=TR+TF基本上是常值,其中,TR为上升沿计算所有事件所需的时间;TF为下降沿计算所有事件所需的时间会产生;当发生系统调用时(比如仿真时的系统函数调用等),额外的延时△t(△t=△t1+△t2),使得当前周期增大为Ts+△t。因此硬件模拟器中的时钟信号周期是无规律变化的,而且受系统调用频度以及系统调用复杂度(即△t的大小)的影响。

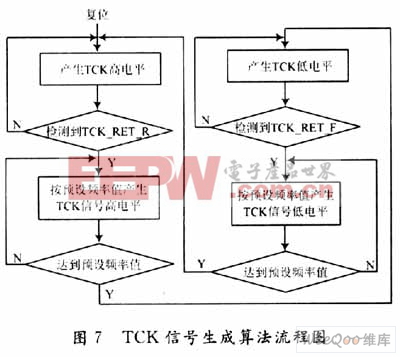

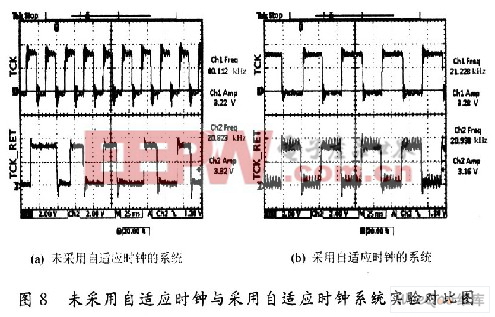

嵌入式处理器的调试系统需要采用系统级的软/硬件协同验证,包括软件开发和调试环境、仿真器系统、处理器系统三部分。在该DSP设计项目中,软件环境(运行在PC机上)和仿真器系统(基于FPGA开发板)都采用真实系统,而DSP则在XtremeⅢ模拟器中实现。仿真器与DSP之间通过JTAG信号进行通信。仿真器采用图3所示的双向同步自适应时钟技术,仿真器发送给DSP的TCK信号特征与图6(a)相同,而DSP反馈给仿真器的同步时钟TCK_RET信号特征与图6(b)相同。因此,在TCK Generator中设计图7所示的算法,从而完全解决了真实硬件系统与硬件模拟器之间的JTAG信号传输时序匹配问题。实验中,设定TCK的工作频率为40 kHz。未采用双向自适应同步时钟技术时,仿真器与xtremeⅢ硬件模拟器之间的JTAG信号传输经常发生TCK_RET时钟沿丢失(等效时钟频率约为20 kHz),导致仿真器无法正确采样TDO数据,如图8(a)所示。采用双向自适应时钟后,尽管整个验证系统中TCK时钟信号的实际工作频率约为20 kHz,但持续不间断工作72 h以上未发现JTAG信号传输错误,从而证明系统能够正常工作,如图8(b)所示。

4 结语

为解决高性能嵌入式处理器或DSP与仿真器之间JTAG信号传输稳定性问题,提出了一种双向同步自适应时钟技术。该技术在同步电路中引入了异步电路的应答机制,巧妙解决了由于嵌入式处理器或DSP(尤其是针对低功耗设计的处理器,它的工作主频会随着负载变化而变化)本身主频变化导致的JTAG信号传输失效。此外,该技术还为软、硬件协同验证中真实系统与硬件模拟器之间信号传输提供了可靠的解决方案。在随后的工作中,将继续研究自适应时钟技术在各种系统跨时钟域信号传输中的应用。从而进一步拓展该技术的适用范围。

评论