基于事件驱动的新型处理器的研究与应用

摘要:针对现代电子设计低成本、高效率、高灵活性的特点,研究了一种新型的处理器:事件驱动多核心处理器。通过对这种处理器基本构架的研究,以及采用新型处理器与采用传统控制器设计差异的对比,分析出该处理器具有性能高、实时性强、易编程等优点。最后,提出了一种新的设计方法:硬件设计软件化,给众多电子系统设计提供新的思路和参考。

本文引用地址:https://www.eepw.com.cn/article/149028.htm关键词:XMOS;事件驱动多核心处理器;硬件线程;硬件设计软件化

0 引言

英国的XMOS Semiconductor公司推出了一种全新的控制器件:事件驱动多核心处理器(以后简称XCore处理器)。凭借一种叫作软件化芯片(Software Defined Silicon)的新技术,XMOS提出了一种革命性的电子设计方法:硬件设计软件化。通过软件设计,可以使用XCore处理器实现以前需要通过FPGA,ASIC实现的硬件性能。这种新的处理器集RISC CPU的效率、DSP的性能和FPGA的灵活性于一体。

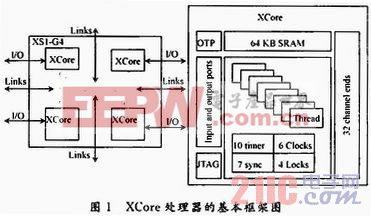

1 XCore处理器的基本构架

图1为XCore处理器的基本框架图。如图所示,每个处理器(以XS1-G4为例)有4个内核(XCore),XCore之间通过一种称之为X-link的技术连接,可以实现XCore之间的数据通信。XCore内部有丰富的硬件资源:8 KB的OTP ROM,64 KB的RAM,10个计算器,6个时钟模块,7个同步单元和4个硬件锁。除此之外,XCore最特别的是具有8个硬件线程和32个通道端(Channel Ends)以及1个事件驱动管理器。每个硬件线程具有独立的专有寄存器组,同时可以访问所在核内的共享硬件资源。

通道(Channel)是线程之间通信的主要方式,一个通道可以连接几个通道端。这样,使用各个通道端的硬件线程就可以相互通信了。通道可以在不同的Xcore之间建立,依托强大的X-link功能,甚至不同处理器之间的线程也可以通过通道进行通信。

2 XCore处理器特点

2.1 硬件多线程技术

硬件多线程技术是XCore处理器能够硬件设计软件化的关键。有别于传统的操作系统实现的多线程,硬件多线程是通过特有的硬件单元来调度。每个硬件线程的时间片精确到1个时钟周期(对应于处理器工作在400 MHz主频的情况下,就是2.5 ns)。传统的操作系统分配给线程的时间片都是在ms级。线程调度的实时性保证了多个硬件线程可以组成高性能的处理流水线。每个Xcore拥有8个硬件线程,如果这个8个线程全部运行,在400 MHz的CPU主频的情况下,理论上可以组成一条8级的主频为50 MHz的流水线;如果处理器内的4个XCore全部运行,则可以组成4条这样的并行流水线。这足以完成大部分中低性能的FPGA实现的功能。

2.2 多功能智能IO模块

多功能智能IO模块是XCore处理器的另一大特色,该模块可以对IO数据进行处理,然后再将数据缓存后送CPU内核处理,这样,可以减轻IO操作对CPU内核的负担。使得流水线设计瓶颈可以缓解。设计者可以适当延长处理流水线每一级的长度,使得软件设计更加灵活,功能更加强大。

多功能智能IO模块具有以下几个功能:端口宽度可编程;带时钟、片选的IO接口;可编程时序IO接口;序列化IO接口;可编程FIFO缓存接口;可编程条件IO接口。灵活运用这些功能,可以轻易的实现MII,ULPI等高速总线接口。

2.3 事件驱动运算

相对于操作系统管理下的软件线程,XCore处理器的硬件线程具有同样的灵活性。每个硬件线程可以被阻塞,当硬件线程被阻塞时处于睡眠状态,它所占用的时钟周期可以释放给其他的硬件线程。举个例子,如果某个XCore以400MHz的工作频率运行8个线程,那么每个硬件线程的实际工作频率是50 MHz。当其中4个线程被阻塞时,剩下的4个硬件线程的工作频率就能够提升到100MHz。当线程被阻塞时,需要等待指定的事件将它唤醒,这些事件可以由定时器、智能IO模块和线程之间通信的通道产生。基于事件驱动运算的机制,可以极大地减少XCore处理器的功耗并显著地提升XCore处理器的效能。

3 实例介绍

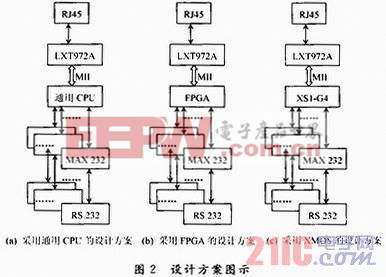

串口服务器是在工业控制领域经常用到的一类设备,其作用是实现UART与以太网之间的协议转换,下面给出了3个不同的设计方案:采用通用嵌入式CPU实现的设计方案;采用FPGA实现的设计方案;以及采用XCore处理器设计方案,如图2所示。

评论