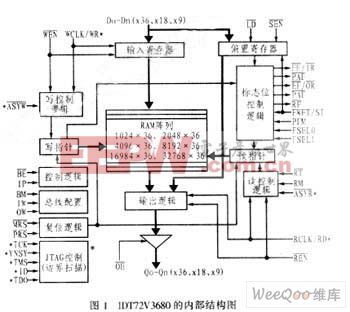

IDT72V3680芯片的内部结构介绍

IDT72V3680属于IDT公司的高密度supersyncTMⅡ36位系列存储器IDT72V3640~3690中的一种,其存储结构为16,384×36。这一系列CMOS工艺的FIFO(先入先出)芯片具有极大的深度。

本文引用地址:https://www.eepw.com.cn/article/148890.htm其基本功能特点如下:

对读/写口都可进行灵活的总线宽度设置,可选择不同的输入/输出数据线宽度(可在36 in 36 out;36 in 18 out;36in 9 out;18 in 36 out;9in 36 out中选择);

重传操作延时很低且固定;

首字的写入到读出的延时很低且固定;

数据密度高达1Mbit;

操作时钟可达166MHz;

可选大/小字节排列格式;

主复位方式可提供FIFO整体清零,部分复位只清掉存储数据,但保留可编程设置项;

几乎空/满标志置位或无效操作可选择同步或异步时间模式;

具有两种时间工作模式,分别为IDT标准模式(采用和标志位)和FWFT首字直传模式(采用标志位);

读写操作采用独立时钟,并可异步操作;

采用TQFP(128引脚)和PBGA(144引脚)两种封装形式,其中PBGA封装形式不仅可用JTAG口提供边界扫描功能,还可选择同步或者异步读写操作(只对PBGA封装);

与5V输入兼容;

具有节电模式;

管脚可与更高密度的芯片IDT72V36100和IDT72V36110兼容。

IDT72V3680的内部结构框图如图1所示。

评论