相变化内存原理分析及设计使用技巧介绍

相变化内存(Phase Change Memory,PCM)是一项全新的内存技术,目前有多家公司在从事该技术的研发活动。这项技术集当今挥发性内存和非挥发性内存两大技术之长,为系统工程师提供极具吸引力的技术特性和功能。工程师无需再费时解决过去几年必须设法克服的所谓内存技术的奇怪特性。因此,当采用NOR或NAND闪存设计系统时,工程师必须掌握许多变通技巧。

本文引用地址:https://www.eepw.com.cn/article/148428.htm由于相变化内存简单易用,设计人员可以把以前的奇怪东西全部忘掉。相变化内存还有助于大幅缩短产品上市时间,提高系统效能和编码容量,降低产品成本。应用设计通常需要RAM内存芯片以补偿闪存的慢速且错综复杂的程序设计协议。在改用相变化内存后,还能降低许多设计对RAM芯片的容量要求,甚至根本不再需要RAM芯片。因此设计人员已经发现在许多设计状况中把现有设计的闪存改由相变化内存取代的确是非常值得一试的。

为什么选用相变化内存

为什么相变化内存很有前景,为什么现在正式接近量产?提出这两个问题有很多理由。时至今日,相变化内存尚未在市场上蓬勃发展的最大原因是,现有内存技术的经济效益远高于任何 新的替代技术。这是每项新技术进入市场时都必须面临的状况,也有许多新技术因而在初引入时被挡在市场大门外。

对于特定的工艺技术,这些替代内存与目前成功的传统竞品相比,不是芯片面积更大,就是晶圆制造成本极高。在向来以成本为王的内存市场上,若想替代现有技术,制造成本高的芯片几乎没有胜算。不过这种局面很快会被打破,因为在今后几年,相变化内存与DRAM的成本差距将会变小。

正面来说,几个原因使得相变化内存在近期引起市场相当大的关注。首先,材料技术在过去十年取得长足进步,现在制造生产相变化内存需要的高纯度薄膜的可行性较以前提高很多。而且,相变化内存需要的硫系材料也取得很多突破性进展,现在被用于大规模制造CD-R和CD-RW光盘。

同时,科学家对这些材料的物理性质的了解也取得相当大的进步。工艺技术节点缩小也发挥了相应的作用:在过去,被加热材料的面积相对较大,改变一次相变化状态需要相当大的能量。随着工艺技术节点缩小,以前像一片海洋的加热材料,现在变得像一个浴盆大小。

最后,业界普遍接受闪存即将达到技术节点极限的观点,也驱动了后续技术研发活动以超越这个极限。尽管闪存升级极限被向后推迟多年,但是所有闪存厂商都承认,闪存无法升级到下一个技术节点的时代很快就会到来,届时闪存产业将必须改变技术。

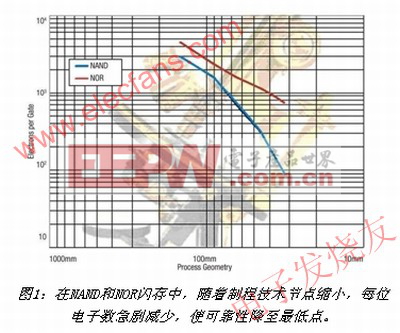

图1描述了闪存升级极限后的现象:储存在一个闪存位内的电子的数量在逐步减少。在大约八年后,当NAND和NOR其中一种闪存升级到10nm工艺节点前,每位所储存的电子数不到10个。

对于一个多级单元架构(MLC),在一个多噪声的环境内,10个电子数量太少,无法储存多位数据,实际要求每位电子数量接近100个,远远高于10个。即使达到这个指标,如此少的电子数量使其很难达到现有应用的可靠性要求。

相变化内存已经上市销售。三星(Samsung)于2004年发布一个PRAM原型,是第一个即将投产的相变化内存。不久之后,恒忆(Numonyx)推出了一个相变化内存原型,在2008年底前,已开始限量出货。从2006年起,BAE系统公司一直在航天航空市场出售C-RAM芯片,这个市场十分关注相变化内存,因为这项技术能够抵抗阿尔法粒子辐射引起的数据位错误。

试用过这些芯片的设计人员表示,当使用比较老的传统的内存技术时,他们必须解决很多技术难题,而这项技术正好能够协助他们根除这些问题。

在一个典型的系统中,非挥发性内存和RAM内存都会被用到,前者用于保存编码,后者用作高速缓存,有时也用于储存其它编码。为了避免使程序员处理不同类型的记忆体,操作系统隐藏了各类内存间的差异,以对其它程序透明的方式,执行对挥发性内存和非挥发性内存的管理任务,而这大大增加了系统的复杂程度。

即便有了这种辅助功能,当使用只读编码储存空间储存编码,以只读数据储存空间储存数据时,程序员还是受限某些限制。如果编码或数据量大于内存的容量,即便超出一个字节,那部分储存空间就必须扩大一倍,导致价格大幅提升。在某些状况下,使用基于相变化内存的系统就可以避免这个问题。

相变化内存改变了游戏规则。编码和数据不必再分开储存在非挥发性内存和RAM的两个容量固定的模块内。编码和数据可以保存在一个内存内。对于小型系统的设计人员,这种方法可以减少芯片数量,降低功耗。读写内存和只读存储器之间不再有固定的界限,对于小型系统和大型系统的设计人员是莫大的福音。

闪存的复杂之处

闪存很难管理。曾有设计工程师形容管理闪存的过程是一种“非常复杂的舞蹈”。曾经采用NAND或NOR闪存设计系统的工程师可以证实这点,闪存管理需要考虑许多因素,例如:损耗均衡、读写同步和坏块管理,这使闪存管理任务变得极其复杂。

与基于闪存的设计相比,相变化内存带来的问题非常少。相变化内存支持位元组修改功能,因此没有NAND和NOR闪存的写入之前需先擦除区块的步骤,因而大幅简化了写入操作。在相变化内存内,逻辑1可以变为逻辑0,反之亦然;所以在写入操作之前无需进行一次擦除操作,相变化内存的写入操作更类似于RAM,而不像NAND或NOR闪存。

相变化内存写入操作速度快,无需NAND或NOR的擦除操作。因此,不再需要同步读写功能,程序设计师几乎不必再写专门的编码,以防止在最新的写入操作附近发生读取操作。

相变化内存的随机寻址类似于NOR或SRAM,非常符合处理器的要求。此外,相变化内存不需要NAND闪存的错误校验功能,因为相变化内存能够保证所有位保存的数据与写入的数据完全相同。

相变化内存根本不需要闪存管理所需的全部算法,例如:损耗均衡和坏块管理。有人称相变化内存是“最适合韧体/软件工程师用的非挥发性内存”。相变化记忆体另外还有一个好处:编码储存区和数据储存区之间的界限比以前更加灵活。在今日的设计中,每个内存应用都需要自己独有的内存拓扑,通常是:

评论