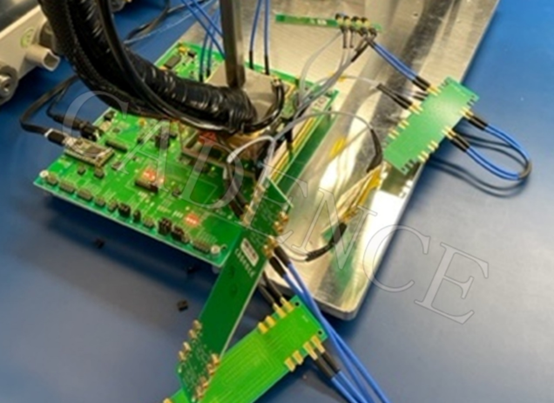

- 3nm 时代来临了!Cadence 在 2023 年 TSMC 北美技术研讨会期间发布了面向台积电 3nm 工艺(N3E)的 112G 超长距离(112G-ELR)SerDes IP 展示,这是 Cadence 112G-ELR SerDes IP 系列产品的新成员。在后摩尔时代的趋势下,FinFET 晶体管的体积在 TSMC 3nm 工艺下进一步缩小,进一步采用系统级封装设计(SiP)。通过结合工艺技术的优势与 Cadence 业界领先的数字信号处理(DSP)SerDes 架构,全新的 112G-ELR

- 关键字:

Cadence TSMC 3nm工艺 SerDes IP

- 2023年5月8日,芯原股份(688521.SH)在互动平台表示,芯原用于人工智能的神经网络处理器IP(NPU)业界领先,已经在10多个领域、60多家客户的110多款芯片中被采用。根据目前市场的需求,芯原基于自身神经网络处理器IP可伸缩可扩展的特性,已发展了覆盖从高性能云计算到低功耗边缘计算的垂直解决方案;同时还推出了从摄像头输入到显示器输出的完整智能像素解决方案。因此,在人工智能领域,芯原的神经网络处理器IP系列产品可广泛适用于包括智慧物联网(AIoT)、智慧汽车、智慧可穿戴、智慧家居、视频数据中心、智

- 关键字:

芯原股份 IP 神经网络处理器IP

- 近日,楷登电子(Cadence)宣布基于台积电3nm(N3E)工艺技术的Cadence® 16G UCIe™ 2.5D先进封装IP成功流片。该IP采用台积电3D Fabric™ CoWoS-S硅中介层技术实现,可提供超高的带宽密度、高效的低功耗性能和卓越的低延迟,非常适合需要极高算力的应用。据悉,楷登电子目前正与许多客户合作,来自N3E测试芯片流片的UCIe先进封装IP已开始发货并可供使用。这个预先验证的解决方案可以实现快速集成,为客户节省时间和精力。

- 关键字:

楷登电子 台积电 N3E UCIe 先进封装 IP

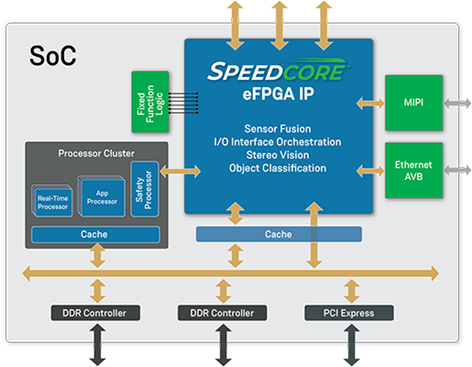

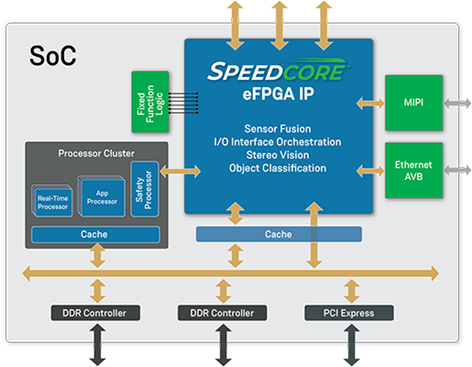

- 提高汽车电气化和自动驾驶的一个主要方面是先进驾驶辅助系统(ADAS)的普及。如今,这些系统正迅速应用于市场上几乎所有的车辆,而且随着技术的成熟,这一趋势只会持续下去。然而,随着技术的发展,ADAS设计人员面临的硬件挑战变得越来越复杂。在本文中,我们将介绍ADAS的硬件需求,FPGA如何填补这些空白,以及为什么eFPGA IP将成为下一个ADAS硬件趋势。ADAS的硬件要求ADAS在现代汽车中的发展给底层硬件带来了一些严峻的挑战。在像ADAS这样的关键任务应用中,最重要的目标是确保车辆乘员的安全。这个目标要

- 关键字:

嵌入式FPGA eFPGA IP ADAS

- 加利福尼亚州坎贝尔 – 2023 年 4 月 12 日 – 致力于加速片上系统(SoC)创建的领先系统 IP 提供商Arteris, Inc.(纳斯达克股票代码:AIP),今天宣布 ASICLAND 已获得具有汽车安全完整性等级 ASIL B 和 AI 选项的Arteris FlexNoC授权。该技术将被用于汽车的主系统总线和各种应用的AI SoC之中。ASICLAND是一家领先的ASIC半导体和SoC设计服务公司。该公司为5nm,7nm,12nm,16nm和28nm处理器开发了许多具有复杂技术的半导体产

- 关键字:

ASICLAND SoC Arteris IP

- 凭借IAR的全新安全解决方案,嵌入式开发人员即使是在软件开发过程的后期阶段,也能轻松地为现有应用植入可靠的安全性,并直接投入生产瑞典乌普萨拉–2023年4月13日–嵌入式开发软件和服务的全球领导者IAR宣布推出IAR Embedded Secure IP解决方案,以帮助开发者即使在产品项目周期的后期,也能够为其固件应用植入嵌入式安全方案。通过IAR Embedded Secure IP解决方案,软件经理、工程师和项目经理可以在设计过程中的任何阶段,甚至是生产和制造阶段,以独特、灵活且安全的方式快速升级他们

- 关键字:

IAR Embedded Secure IP 开发后期安全性

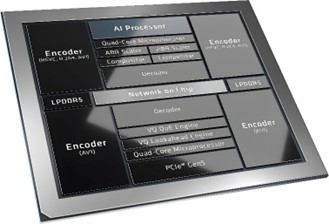

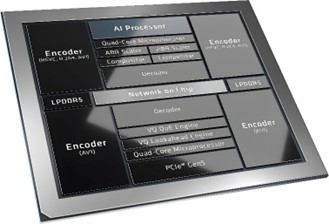

- 2023 年 4 月 6 日,加利福尼亚州圣克拉拉 — AMD (超威,纳斯达克股票代码:AMD)今日宣布推出 AMD Alveo™ MA35D 媒体加速器,该卡具备两个 5 纳米基于 ASIC 的、支持 AV1 压缩标准的视频处理单元( VPU ),专为推动大规模直播互动流媒体服务新时代而打造。随着全球视频市场超 70% 的份额由直播内容主导1,一类新型的低时延、大容量交互式流媒体应用正在涌现,例如连线观赏、直播购物、在线拍卖和社交流媒体。 AMD Alveo MA35D 媒体加速器Alveo

- 关键字:

AMD 5nm ASIC 媒体加速器卡 大规模交互式流媒体服务

- 2月23日,半导体IP企业芯原股份公布2022年年度业绩快报,报告期内,公司预计实现营业收入26.79亿元,同比增长25.23%;预计实现归属于母公司所有者的净利润7381.43万元,同比增长455.31%。芯原股份表示,2022年度,在半导体产业周期的景气度转换、下行压力增大的产业背景下,公司保持了营业收入同比快速增长趋势。其中知识产权授权使用费收入预计同比增长28.79%、特许权使用费收入预计同比增长12.49%、芯片设计业务收入预计同比增长4.46%、量产业务收入预计同比增长36.41%。2022年

- 关键字:

IP 芯原股份

- 亮点: ● 第五代片上网络互连硅IP技术● 与手动物理迭代相比,物理收敛速度快5倍● 使客户能够在时间进度和预算限制内实现PPA目标致力于加速片上系统(SoC)创建的领先系统 IP 提供商Arteris, Inc.(纳斯达克股票代码:AIP)今天宣布,推出 Arteris FlexNoC 5 物理感知片上网络(NoC)互连 IP。FlexNoC 5 使 SoC 架构团队、逻辑设计人员和集成商能够整合跨功耗、性能和面积(PPA

- 关键字:

Arteris FlexNoC 5 物理感知片上网络 IP

- 倍捷连接器(PEI-Genesis)总裁兼首席执行官Steven Fisher正式宣布收购有40年历史,总部位于加州的连接、被动、和机电元器件(IP&E)供应商Testco Inc.,。Steven Fisher表示:“此次收购将为客户提供更广泛的IP&E产品方案。我们是行业值得信赖的互连专家,本次收购有助于提升我们解决互连问题的能力,更丰富的产品和服务,会进一步加强我们和客户的合作。”40年以来,Testco Inc. 为全球科技公司提供连接、被动、和机电元器件(IP

- 关键字:

倍捷连接器 IP&E Testco

- 过去几年,国际形势的变化让壮大中国芯片设计产业成为中国半导体产业发展的主题,伴随着全社会对中国半导体产业的关注提升和资本的涌入,整个半导体设计产业链迎来全面的发展机遇。对中国集成电路设计产业来说,芯片设计能力的提升,不仅需要设计公司技术的提升,还需要先进的本土芯片制造能力和相关设计工具的鼎力支撑。 随着国内芯片设计企业的大量涌现,本土芯片设计带动着设计IP需求增长非常明显,这不仅给成立多年的本土IP企业发展的黄金机遇,同时也催生出大量的新兴IP初创企业,这些企业的起点高、IP运作经验丰富,共同

- 关键字:

芯来科技 RISC-V IP ICCAD

- 过去几年,国际形势的变化让壮大中国芯片设计产业成为中国半导体产业发展的主题,伴随着全社会对中国半导体产业的关注提升和资本的涌入,整个半导体设计产业链迎来全面的发展机遇。对中国集成电路设计产业来说,芯片设计能力的提升,不仅需要设计公司技术的提升,还需要先进的本土芯片制造能力和相关设计工具的鼎力支撑。 随着国内芯片设计企业的大量涌现,本土芯片设计带动着设计IP需求增长非常明显,这不仅给成立多年的本土IP企业发展的黄金机遇,同时也催生出大量的新兴IP初创企业,这些企业的起点高、IP运作经验丰富,共同为

- 关键字:

奎芯科技 Chiplet IP ICCAD

- 德国慕尼黑,2022年12月7日——处理器设计自动化和RISC-V处理器IP的领导者Codasip今日宣布成立Codasip实验室(Codasip Labs)。作为公司内部创新中心,新的Codasip实验室将支持关键应用领域中创新技术的开发和商业应用,覆盖了安全、功能安全(FuSa)和人工智能/机器学习(AI/ML)等方向。该实验室的使命在于识别和构建相关技术,以扩展定制计算的可能性,并加快具有定制化的、领域专用设计的差异化产品的开发,并缩短其上市时间。Codasip实验室将由公司创始人兼总裁马克仁(Ka

- 关键字:

Codasip Codasip 实验室 IP RISC-V

- 加利福尼亚州埃尔多拉多山,2022年12月9日-为AI和IoT提供嵌入式计算硬件和软件的边缘AI解决方案提供商-安提国际(Aetina)推出了一种基于ASIC的全新边缘AI系统。该系统由可编程Blaize®Pathfinder P1600嵌入式系统模块(SoM)提供支持。Aetina AI推理系统-AIE-CP1A-A1是一款小型嵌入式计算机,专为不同的计算机视觉应用而设计,包括物体检测、人体运动检测和自动检测。 AIE-CP1A-A1采用小尺寸Blaize®Pathfinder P1600嵌入

- 关键字:

安提国际 Aetina Blaize ASIC 边缘AI系统

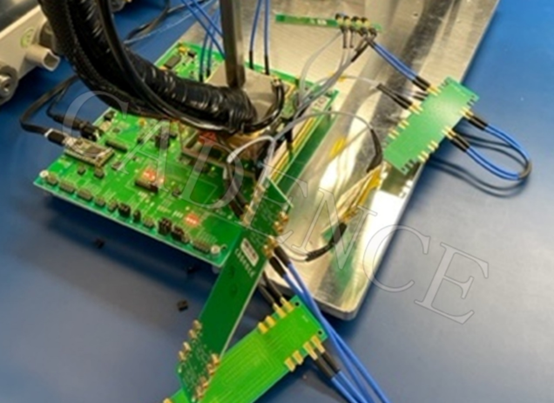

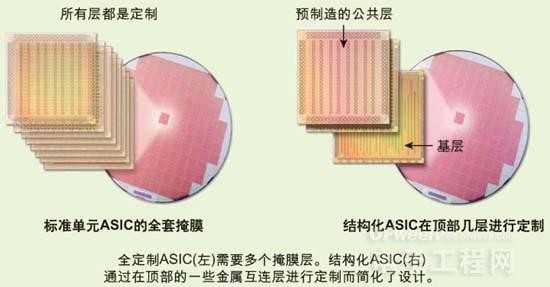

- 技术改良一直走在行业进步的前沿,但世纪之交以来,随着科技进步明显迅猛发展,消费者经常会对工程师面临的挑战想当然,因为他们觉得工程师本身就是推动世界进步的中坚力量。作为世界创新的幕后英雄,特别是在电子器件和通信技术方面,工程师们要开发测试设备,验证这些新技术,以把新技术推向市场。这些工程师必须运行尖端技术,处理预测行业和创新未来的挑战。在开创未来的过程中,测试测量工程师面临的基础性创新挑战之一,是确定设计中采用专用集成电路(ASIC)还是现场可编程门阵列(FPGA)。突破创新中采用ASIC的优势和挑战在历史

- 关键字:

测试测量 ASIC FPGA

asic ip介绍

您好,目前还没有人创建词条asic ip!

欢迎您创建该词条,阐述对asic ip的理解,并与今后在此搜索asic ip的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473