- 作者序:2005年应中国电子报邀请,我和马启元(董事长)博士写了一篇类似文章。回过头看确实有意义。故再用闲暇时间,应半导体产业纵横(ICVIEWS)邀请做一篇展望文章,以其对某些读者可能有用。从2014年开始,我国政府开始鼓励国内半导体发展,这是继2000年18号文件出台以来,给予集成电历史上最强劲的支持,包括大基金及各种风险投资。此后,2018年开始我国的芯片制造、设计、材料、装备等围绕IC的企业群起,并呈现“多点开花”的局面。一时间“遍地英雄下夕烟”,争相拼抢中国巨大的IC市场。与此同时,国外名牌企业

- 关键字:

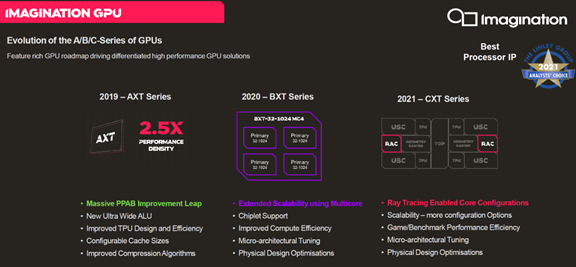

SoC ASIC

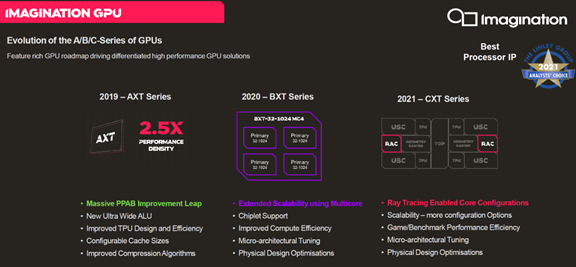

- 过去50余年,芯片制程迭代沿着摩尔定律滚滚向前,并持续增强着芯片的算力与性能。现如今,无论是在SoC上集成越来越多的功能模块,又或是利用chiplet技术在先进制程下进一步提升芯片集成度,都充分展现了芯片性能、功耗和成本的改进不能仅仅依赖于制程的升级,而需从不同的维度拓展创新来延续摩尔定律的“经济效益”。这导致芯片设计变得越来越困难,IP的作用也愈加凸显,逐渐成为企业寻求设计差异化道路上的“秘钥”。 日前,在深圳举办的第10届EEVIA年度中国硬科技媒体论坛暨产业链研创趋势展望研讨会上,Imag

- 关键字:

IP Imagination

- 在庞大的半导体细分产业链中,IP是其中最特殊的一环。正是借助众多的IP,才让半导体发展的步伐如此之快。IP是整个半导体上游产业链里面的核心,根据统计数据可以发现,每一元芯片能撑起200多元的社会经济,而每一元的IP,能支持20000元的社会经济价值,所以IP公司的存在是必要的。 随着芯片复杂度不断提升,特别是芯片进入SoC时代使得系统对各个环节技术要求越来越高,对一些中小型公司、创业公司来说,他们需要在成长过程中专注核心领域,没办法提供整个SoC完整的技术,所以它需要IP公司的支持,IP公司能协

- 关键字:

Imagination SoC IP GPU

- 中国上海—2022年10月14日——一站式定制芯片及IP供应商——灿芯半导体日前宣布推出可用于客制化ASIC/SoC设计服务的MIPI IP完整解决方案。该解决方案由一系列 MIPI控制器和PHY构成。可以帮助系统制造商和IC公司等设计高质量的ASIC/SoC产品,同时加速上市时间。 MIPI联盟在2003年成立,MIPI全称Mobile Industry Processor Interface,即移动产业处理器接口。顾名思义,是为了统一和简化手机处理器的接口,CSI、DSI、DigRF、C/D

- 关键字:

灿芯 MIPI IP

- 全球领先的无线连接和智慧感测技术及共创解决方案的授权许可厂商CEVA推出了PentaG-RAN,这是业界首个用于ASIC的5G基频平台IP,针对基地站和无线电配置中的蜂巢式基础设施。这款IP包括分布式单元(DU)和远程无线电单元(RRU),涵盖从小基站到大规模多输入多输出(mMIMO)范围。这款异构基频计算平台将为有意开拓Open RAN(O-RAN)设备市场的企业大幅降低进入壁垒。数字化转型不断要求更高的蜂巢带宽和更低的延迟,推动5G基地站和无线电ASIC市场蓬勃发展。最近,Open RAN提倡和mMI

- 关键字:

CEVA 5G RAN ASIC

- ● PentaG-RAN弥补半导体行业设计差距,为企业优化ASIC 解决方案以挺进利润丰厚的 5G Open RAN设备市场● 突破性平台架构通过完整L1 PHY解决方案应对大规模MIMO计算难题,与现有的FPGA和商用现货CPU 替代方案相比,节省功耗和面积高达10倍● PentaG-RAN客户可享用CEVA共创服务,以开发整个 PHY 子系统直至完成芯片设计全球领先的无线连接和智能感知技术及共创解决方案的授权许

- 关键字:

CEVA 5G RAN ASIC 基带平台IP

- 加利福尼亚州圣克拉拉市,2022年9月19日——高性能现场可编程逻辑门阵列(FPGA)和嵌入式FPGA(eFPGA)半导体知识产权(IP)领域的领导性企业Achronix半导体公司宣布:该公司已经收购了Accolade Technology的关键IP资产以及Accolade的技术团队,此举使Achronix的客户能够更快速且更轻松地设计高性能网络和数据中心系统。Accolade在FPGA的网络应用方面拥有深厚的专业知识,此次收购使Achronix能够为开发网络技术的客户提供强大的硬件和软件解决方案。“如今

- 关键字:

Achronix FPGA Accolade IP

- 一站式定制芯片及IP供应商——灿芯半导体日前宣布推出可用于ASIC/SoC的USB IP完整解决方案。该解决方案由一系列 USB 控制器和 PHY 构成,可以助力系统制造商、个人电脑原始设备制造商和 IC公司等设计高质量的ASIC/SoC 产品。USB(通用串行总线)已经非常成功地将打印机、扫描仪、键盘、鼠标、闪存驱动器、操纵杆、相机和显示器等硬件连接到各种计算机,包括智能手机、台式机、平板电脑和笔记本电脑等。USB4规范在2019年9月由USB-IF组织执行,可支持USB3、Displayport、PC

- 关键字:

灿芯 USB IP

- 全球领先的无线连接和智能感知技术及共创解决方案的授权许可厂商CEVA, Inc.(纳斯达克股票代码:CEVA)宣布,包含CEVA IP的并支付权利金的芯片的累计出货量已经在第二季超过了150亿颗。在上市将近二十周年之际,CEVA达成了这一重要里程碑。实现前100亿颗CEVA助力的芯片出货花费了超过15年时间,而完成随后50 亿颗芯片出货则只用了不到三年半。 CEVA IP在物联网时代以令人惊讶的速度被广泛采用也证实了CEVA在无线连接的普及方面发挥了重要的作用。CEVA将5G、蜂窝物联网、蓝牙、

- 关键字:

CEVA IP

- Credo Technology(纳斯达克股票代码:CRDO)近日正式宣布推出其基于台积电5nm及4nm制程工艺的112G PAM4 SerDes IP全系列产品,该系列能够全面覆盖客户在高性能计算、交换芯片、人工智能、机器学习、安全及光通信等领域的广泛需求,包括:超长距(LR+)、长距(LR)、中距(MR)、超极短距(XSR+)以及极短距(XSR)。 Credo IP产品业务开发助理副总裁Jim Bartenslager表示, “Credo先进的混合信号以及数字信号处理(DSP)1

- 关键字:

Credo 台积电 5nm 4nm SerDes IP

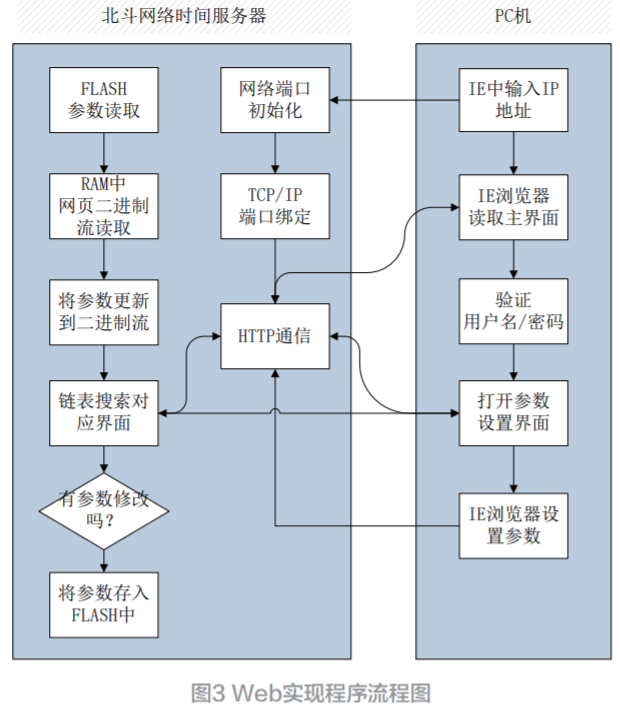

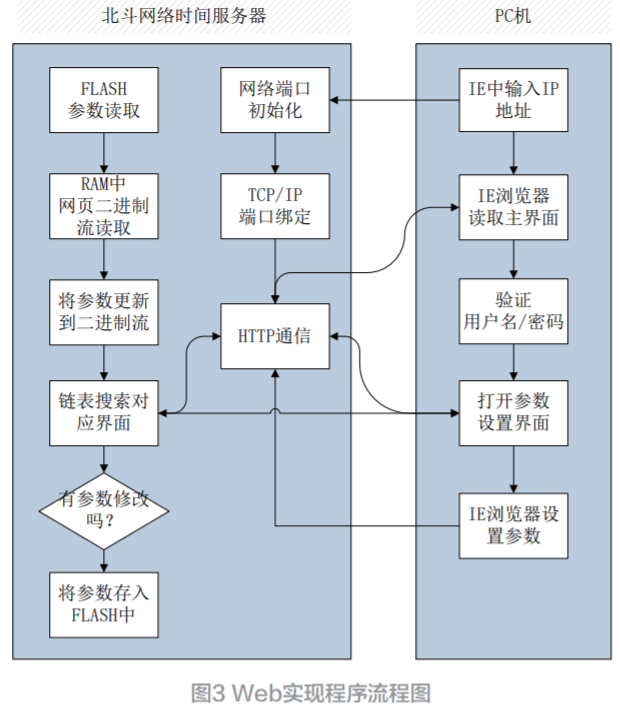

- 摘要:本文介绍了嵌入式北斗网络时间服务器的基本功能,重点讲述了如何在该设备中添加Web网页的方法

及实现过程,以及在嵌入式设备中添加此功能应该考虑的资源因素。关键词:TCP/IP;HTTP;Cortex-M4;RAM;链表 1 时间服务器功能描述北斗卫星接收终端接收北斗导航卫星发射的 RNSS

(Radio Navigation Satellite System,无线导航卫星系统)

无线电波信号,在设备内部通过 PVT 解算,计算出用

户当前的位置、速度以及时间信息。北斗的时间信息具

- 关键字:

202208 TCP/IP HTTP Cortex-M4 RAM 链表

- Inuitive™ 和业界领先的提供片上网络(NoC)互连和IP部署软件以加快系统级芯片(SoC)创建的系统IP供应商 Arteris® Inc.今天宣布,Inuitive 已为其下一代计算机视觉平台部署了 Arteris FlexNoC® 互连 IP。该技术解决了连接和时序收敛的挑战,可以实现先进的下一代前沿视觉处理器所需的激进性能目标。这些先进的 SoC 将扩展多核视觉处理并增强高质量的深度传感。这些芯片将部署在 3D 深度成像、物体识别和跟踪,以及其他使用计算机视觉算法的各种应用中,比如增强现实、虚

- 关键字:

Arteris IP 视觉处理器

- 一站式定制芯片及IP供应商——灿芯半导体日前宣布推出用于高速DDR物理层中的Zero-Latency (零延迟)和True-Adaptive(真自适应)两项技术。这两项技术已经开始在12/14 FinFET, 22/28nm的DDR4/LPDDR4,4x高性能物理层IP上进行部署,将为客户带来更高效、更稳定的全新体验。 Zero-Latency (零延迟) 技术在读数据通路上,采用了两种可选的、独特的采样方式进行数据转换,而不像其他DDR物理层供货商采用FIFO进行跨时钟域转换,此技术将延迟降低

- 关键字:

灿芯 DDR IP

- 可定制RISC-V处理器知识产权(IP)和处理器设计自动化的领导者Codasip日前宣布,Veridify Security公司的抗量子安全工具现在可以通过安全启动功能支持Codasip的RISC-V处理器。在固件加载到Codasip处理器上时,Veridify的安全算法就会对其进行验证,以使RISC-V开发人员确信嵌入式系统是安全可用的。Veridify的安全启动功能是基于一种比传统加密方法运行速度更快的算法;只需要很小的代码空间和超低功耗,非常适合Codasip的低功耗嵌入式处理器系列。通过使用Ver

- 关键字:

Codasip RISC-V IP

- 新闻重点:· 全新旗舰产品 Immortalis GPU 将显著优化安卓游戏体验,并首次推出基于硬件的光线追踪功能· 最新 Armv9 CPU 将峰值和效率性能提升至全新水平· 新的 Arm 全面计算解决方案 (Total Compute Solutions) 可满足各级别的性能、效率和可扩展

- 关键字:

arm IP 移动游戏

asic ip介绍

您好,目前还没有人创建词条asic ip!

欢迎您创建该词条,阐述对asic ip的理解,并与今后在此搜索asic ip的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473