ARM存储器之:存储管理单元MMU

⑤域控制位失效

域控制位失效包括两种类型。一种基于段的存储访问域控制失效。在一级描述符中包含4位的域标识符。该标识符指定了本段所属的域,在MMU读取一级描述符时,它检查域访问控制寄存器c3中对应于该域的控制位,如果相应的两位控制位为0b00,说明该域不允许存储访问,这时,就产生了基于段的存储访问域控制失效。第二种是基于页的存储访问中域控制位失效。在一级描述符中包含4位的域标识符。该标识符指定了本页所属的域,在MMU读取一级描述符时,它检查域访问控制寄存器c3中对应于该域的控制位,如果相应的两位控制位为0b00,说明该域不允许存储访问,这时就产生了基于页的存储访问域控制失效。

⑥访问权限失效

访问权限失效的检查是在域控制位失效检查时进行的。这时如果域访问控制器中对应于该域的控制位为0b01,则要进行相应的权限检查。访问权限失效有两种类型。一种基于段的存储访问权限控制失效,对于基于段的存储访问,在一级描述符中包含一个两位的访问权限控制位AP。如果字段AP标识了不允许进行相关存储访问时,产出基于段的存储访问权限控制失效。第二种是基于页的存储访问控制失效。对于基于页的存储访问,在二级描述符中定义的可能为大页、小页或者微页。当二级描述符中定义的为微页时,该二级描述符中包含一个对应于该微页的访问控制字段AP,如果字段AP标识了不允许进行相关的存储访问,这时产生基于子页的存储访问权限控制失效。同样,当二级页表描述符中定义的为小页或大页时,操作过程同微页。

(3)外部存储访问失效

除处理器内部MMU向CPU报告错误外,ARM体系结构还定义了一个外部访问中断引脚。该引脚可以用于外部存储器向CPU访问失效异常。但是,并不是所有失效异常都可以通过这种方式报告,所以该引脚在连线时要非常注意。下面列举了存储访问操作,可以通过这种机制中止和重启动。

·读操作(reads)。

·非缓存的写操作(unbufferedwrites)。

·一级描述符预取(first-leveldescriptorfetch)。

·二级描述符预取(second-leveldescriptorfetch)。

·非缓存的信号量操作(semaphoresinuncachable/unbufferablememoryareas)。

在Cache预取时,可以在任意字时终止存储访问过程。如果存储访问发生在存储器想要获取的数据中,这时该存储访问将立即被中止。如果产生中止的数据是在Cache预取时,从存储器顺序读出的,那么直到这些数据被存储器访问时,该存储访问才会被中止。

带缓存的写操作不能通过这种方式向CPU报告异常。因此,在系统中标记为可外部中止的存储区域不要进行可缓存的写操作。

15.5.9快速上下文切换扩展(FCSE,FastContextSwitchExtension)

(1)快速上下文切换扩展原理

快速上下文切换扩展(FCSE,FastContextSwitchExtension)是MMU中的一个附加硬件,用于提高ARM嵌入式系统的系统性能。FCSE使得多个独立任务可以运行在一个固定的重叠存储空间中,而在上下文切换时,不需要清理(clean)或清除(flush)Cache和TLB。FCSE主要特征就是不需要清除Cache和TLB。

通常情况下,如果两个进程占有的虚拟地址空间有重叠,系统在两个进程之间进行切换时,必须进行虚拟地址到物理地址的重映射。而虚拟地址到物理地址重映射涉及到重建MMU中页表,而且Cache及TLB中的内容都必须使无效。这样操作将带来巨大的系统开销,一方面重建MMU和使无效Cache及TLB的内容需要很大的开销,另一方面重建Cache和TLB内容也需要很大的开销。

快速上下文切换扩展的引入避免了这种开销。它位于CPU和MMU之间,如果两个进程使用了同样的虚拟地址空间,则对CPU而言,两个进程的空间地址是一样的。快速上下文切换扩展对各进程的虚拟地址进行变换,这样系统中CPU之外的部分看到的是经过快速上下文切换扩展变换的虚拟地址。快速上下文切换扩展将各进程的虚拟空间变换成不同的虚拟空间。这样在进行进程间切换时就不需要进行虚拟地址到物理地址的重映射。

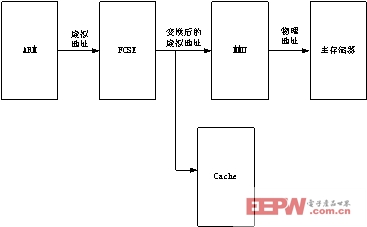

快速上下文切换扩展将CPU发出的每个虚拟地址按照上述的规则进行变换,然后发送到系统中的其他部分。变换过程如图15.37所示。

图15.37快速上下文切换扩展变换过程

使用快速上下文切换扩展,虚拟存储管理增加了一次地址转换。快速上下文切换扩展在虚拟地址到达Cache和TLB前,使用一个特殊的、包含进程ID值的重定位寄存器来修改虚地址。把第一次变换前的地址称为虚地址VA(VirtualAddress),把第一次变换后的地址称为修改后虚拟地址MVA(ModifiedvirtualAddress)。

这样,任务间的切换就不用涉及到改变页表,只需简单地将新任务的进程ID写到位于CP15地FCSE进程ID寄存器。正是因为任务切换不需要改变页表,因而切换后Cache和TLB中的值依然保持有效,不需要清除。

ARM系统中,4GB的虚拟空间被分为128个进程空间快,每个进程空间块大小为32MB。每个进程空间块中可以包含一个进程,该进程可以使用虚拟地址空间0x00000000~0x01ffffff,这个地址范围也就是CPU看到的进程的虚拟空间。系统128个进程空间块的编号为0~127,编号为1的进程空间块中的进程实际使用虚拟地址空间为1×0x02000000~1×0x02000000+0x01ffffff。这个地址空间是系统中除CPU之外的其他部分看到的该进程所占有的虚拟地址空间。

由地址VA到MVA的变换算法如下所示。

MVA=VA+(ox02000000×进程ID)

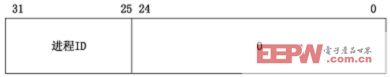

保存在CP15寄存器c13寄存器中的值包含进程ID,c13中从bit[31]~bit[25]共7位标识进程ID,因此可以有128个进程。寄存器格式如图15.38。

图15.38快速上下文切换寄存器c13

访问寄存器c13的指令格式如下所示:

MCRp15,0,Rd>,c13>,c0,0

MRCp15,0,Rd>,c13>,c0,0

其中,在读操作时,结果中位[31:25]返回PID,其他位的数值是不可预知的。写操作将设置PID的值。

当PID=0时,MVA=VA,相当于禁止了FCSE。系统复位后PID为0。

当正在运行的进程访问别的进程时,被访问的进程标识不能为0。这时,CPU发生的地址VA的高7位不是全0。

完整的VA到MVA的变换算法如下所示。

If(VA[31:25]==0b0000000)then

MVA=VA|(PID<<25=

Else

MVA=VA

存储器相关文章:存储器原理

评论