ARM存储器之:存储管理单元MMU

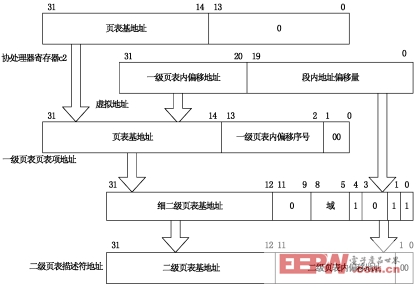

基于细二级页表的地址变换过程如图15.29所示。

(7)基于二级页表的地址变换过程

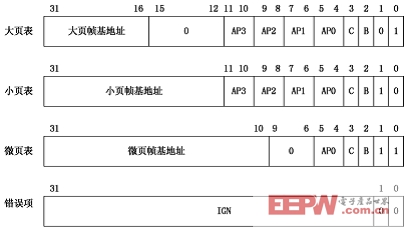

二级页表有4种可能的页表项:

·定义64KB页帧属性的大(Large)页表项;

·定义4KB页帧属性的小(Small)页表项;

·定义1KB页帧属性的微(tiny)页表项;

·访问中止异常的错误项。

系统通过页表项的最低位[1:0]来确定页表项的类型。二级页表的页表项格式如图15.30所示。

当bits[1:0]=0b01时,该页表项为大页表项,它包含了一个64KB物理存储块的基地址。如果页表是细二级页表,那么大页表项将在表中重复64次;如果页表是粗二级页表,那么大页表项将在表中重复16次。

图15.29基于细二级页表的地址变换过程

图15.30二级页表的页表项格式

当bits[1:0]=0b10时,该页表项为小页表项,它保存一个4KB物理存储块的基地址。如果页表是细二级页表,那么小页表项将在表中重复4次;如果页表是粗二级页表,那么大页表项只需在表中出现1次。

当bits[1:0]=0b11时,该页表项为微页表项,它保存一个1KB物理存储块的基地址。如果页表是细二级页表,那么微页表项只需在表中重复1次;微页表项不会出现在粗二级页表中,如果出现,那么访问结果不可预知。

当bits[1:0]=0b00时,该页表项产生存储页访问错误。错误条件会导致预取指中止或数据中止,这取决于具体的存储器访问类型。

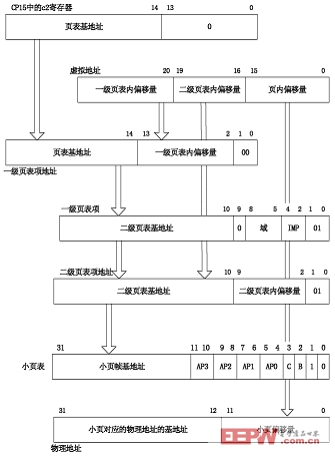

(8)大页表描述符及其地址变换过程

如果二级页表项bits[1:0]=0b01,说明该页表项为大页表项,它不仅包含了一个64KB物理存储块基地址,同时还含有4组权限位域以及页的Cache和写缓存属性。每一组访问权限域代表虚存页的1/4,这些页表项可以看成是16KB子页,以更好的控制64KB页的访问权限。

具体定义如表15.26所示。

表15.26 大页表项中各字段含义

字段 | 含义 |

bits[1:0] | 大页表项类型标识符 |

bits[3:2] | Cache和写缓存属性 |

bits[11:4] | 访问权限控制位,具体编码见表15.27。 一个大页分为4个子页 AP0子页0的访问权限 AP1子页1的访问权限 AP2子页2的访问权限 AP3子页3的访问权限 |

bits[15:12] | 当前未使用,应为0 |

bits[31:16] | 该大页对应的物理页帧的基地址的高16位 |

图15.31说明了基于大页表的地址变换过程。

图15.31基于大页表的地址变换过程

(9)小页表描述符及其地址变换过程

如果二级页表项bits[1∶0]=0b10,说明该页表项为小页表项,它不仅包含了一个4KB物理存储块基地址,同时还含有4组权限位域以及页的Cache和写缓存属性。每一组访问权限域代表虚存页的1/4,这些页表项可以看成是1KB子页,以更好的控制4KB页的访问权限。

页表项的具体定义如表15.27所示。

表15.27 小页表项中各字段含义

字段 | 含义 |

bits[1:0] | 小页表项类型标识符 |

bits[3:2] | Cache和写缓存属性 |

bits[11:4] | 访问权限控制位,具体编码见表15.22。 一个小页分为4个子页 AP0子页0的访问权限 AP1子页1的访问权限 AP2子页2的访问权限 AP3子页3的访问权限 |

bits[15:12] | 当前未使用,应为0 |

bits[31:16] | 该小页对应的物理页帧的基地址的高20位 |

图15.32说明了基于小页表的地址变换过程。

图15.32基于小页表的地址变换过程

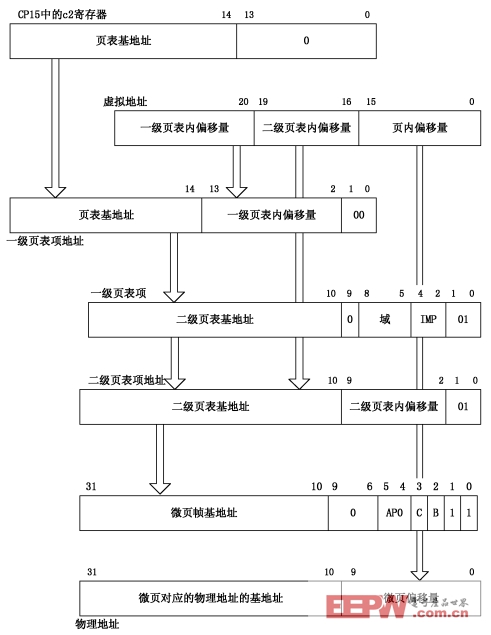

(10)微页表描述符及其地址变换过程

如果二级页表项bits[1∶0]=0b11,该二级页表项是微页表项,它提供了一个1KB物理存储块的基地址,同时含有一个访问权限位域以及页的Cache和写缓存属性。微页表项的具体含义如表15.28所示。

表15.28 微页表项中各字段含义

字段 | 含义 |

bits[1:0] | 微页表项类型标识符 |

bits[3:2] | Cache和写缓存属性 |

bits[5:4] | 访问权限控制位,具体编码见表15.29 |

bits[9:6] | 当前未使用,应为0 |

bits[31:10] | 该微页对应的物理页帧的基地址的高22位 |

图15.33说明了基于微页表的地址变换过程。

图15.33基于微页表的地址变换过程

存储器相关文章:存储器原理

评论