ARM存储器之:存储管理单元MMU

下面的例子显示了一个使TLB无效的过程。

【例】一个使TLB无效的过程。

MOVr1,0;

MCRp15,0,r1,c8,c7,0

(2)锁定TLB

由于对TLB表的查询经常会使系统访问内存(要查询的段、页不在TLB中),这就使得系统的平均访问时间大大增加。对于实时系统,就需要将一些关键的页表项锁定在访问速度相对较快的TLB中。

ARM920T、ARM922T、ARM926EJ-S、ARM1022E和ARM1026EJ-S内核版本支持TLB转换数据的锁定。如果TLB中的某一行是锁定的,则当TLB清除命令发出时,它仍然保留在TLB中。

与TLB锁定相关的操作可以通过对CP15寄存器r10编程来实现。

各种ARM核的可用锁定命令如表15.31所示。

表15.31 访问TLB锁定寄存器的命令

命令 | MCR指令 | Rd的值 | 支持的内核 |

读数据TLB锁定寄存器 | MRCp15,0,Rd,c10,c0,0 | TLB锁定 | ARM920T、ARM922T、ARM926EJ-S、ARM1022E、ARM1026EJ-S、StrongARM、Xscale |

写数据TLB锁定寄存器 | MCRp15,0,Rd,c10,c7,1 | TLB锁定 | ARM920T、ARM922T、ARM926EJ-S、ARM1022E、ARM1026EJ-S、StrongARM、Xscale |

读指令TLB锁定寄存器 | MRCp15,0,Rd,c8,c5,0 | TLB锁定 | ARM920T、ARM922T、ARM926EJ-S、ARM1022E、ARM1026EJ-S、StrongARM、Xscale |

写指令TLB锁定寄存器 | MCRp15,0,Rd,c8,c5,1 | TLB锁定 | ARM920T、ARM922T、ARM926EJ-S、ARM1022E、ARM1026EJ-S、StrongARM、Xscale |

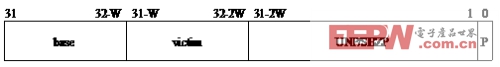

其中Rd的格式如图15.35所示。

图15.35Rd格式详解

其中,

·W=log2N,N为TLB中入口(entry)的个数。对ARM920T、ARM922T、ARM926EJ-S、ARM1022E版本的内核来讲,W=6;而对于ARM1026EJ-S内核版本,W=3。

·victm位域:确定下次被换出的TLB入口(entry)。

·base位域:从第0个入口(entry)到base−1入口的TLB值,被锁定。

锁定TLB中N条地址入口的操作序列如下。

①确保在整个锁定过程中不会发生异常中断,可以通过禁止中断等方法实现。

②如果锁定的是指令TLB或指令/数据统一的TLB,将base=N、victim=N、P=0写入寄存器c10。

③使整个将要锁定的TLB无效。

④如果要锁定指令TLB,确保与锁定过程有关的指令地址变换地址入口已经加载到指令TLB中。

| 注意 | 在此过程中,TLB的一个地址变换入口可以涵盖所有与锁定TLB相关的指令。这通常是由使整个TLB无效后的第一条指令实现的。 |

如果要锁定的是数据TLB,确保与锁定过程有关的数据地址变换地址入口已经加载到数据TLB中。

| 注意 | 在此过程中避免使用内嵌语法(inlineliteral)。所有锁定TLB用到的数据可以被TLB中一个地址变换条目所覆盖。 |

如果系统使用统一的数据TLB和指令TLB,上述两条都要保证。

⑤对于I=0到N,重复执行下列操作:

·将base=I、victim=I、P=1写入寄存器c10中;

·将每一条想要锁定到TLB的变换地址入口读取到TLB中。对于数据TLB和数据/指令统一的TLB可以使用LDR指令读取一个涉及该变换地址入口的数据,将该地址变换入口读取到TLB中。对于指令TLB,通过操作寄存器c7,将相应的变换地址读取到指令TLB中。

⑥将base=N、victim=N、P=0写入寄存器c10中。

要解除TLB中被锁定的变换地址入口,可以使用下面的操作序列。

①通过操作寄存器c8,使TLB中各被锁定的变换地址入口无效。

②将base=0、victim=0、P=0写入寄存器c10中。

15.5.8存储访问失效

ARM中有两种存储访问失效(Fault)可以导致处理器停止执行。

·MMU失效(MMUFault):由MMU检测到失效(Fault)并通知处理器。

·外部存储器访问中止(ExternalAbort):由外部存储器向存储器报告无效的存储器访问请求。

上述两种情况统称为存储访问中止(Abort)。如果存储访问中止发生在数据访问周期,CPU将产生数据访问中止异常中断(DataAbort);如果存储访问发生在指令预取周期,当该指令执行时,CPU产生指令预取异常中断(PrefetchAbort)。

| 注意 | 预取指令时发生错误,只有当该指令执行时,CPU才会产生指令预取异常中断。 |

(1)MMU失效

MMU可以产生4种类型的访问失效,分别是:

·地址对齐失效(AlignmentFault);

·地址变换失效(TranslationFault);

·域控制失效(DomainFault);

·访问权限控制失效(PermissionFault)。

存储系统可以中止3种类型的存储访问:

·Cache行预取(linefetch);

·无Cache和写缓存的存储器访问(uncachedorunbufferedaccesses);

·传输表访问(translationtableaccesses)。

MMU失效优先于外部存储器访问中止请求。当存储访问失效发生时,系统控制协处理器中有两个寄存器分别负责保存发生中止的失效状态和地址。

| 注意 | 如果一条指令在预取阶段发生错误,它仍将进入指令流水线,直到该条指令被执行时,预取异常才发生。但当预取错误指令在进入执行阶段前,指令发生跳转,那么该预取异常不会发生,协处理器错误寄存器的状态也不会被更新。 |

(2)MMU中与存储访问失效相关的寄存器

MMU中与存储访问失效相关的寄存器有两个:

·失效状态寄存器(FSR,FaultStatusRegister);

·失效地址寄存器(FAR,FaultAddressRegister)。

失效状态寄存器是协处理器寄存器c5。失效地址寄存器为协处理器寄存器c6。

当存储访问失效发生时,失效状态寄存器中的字段被更新以反映所发生的存储访问失效的相关的信息,包括存储访问所属的域以及存储访问的类型。同时存储访问失效的虚拟地址被保存到地址寄存器c6中。

在数据访问周期发生存储访问失效更新了失效状态寄存器后,如果系统尚未进入存储异常模式,这时发生了指令预取引起的存储失效,则该指令预取引起的访问失效将不会更新失效状态寄存器的值。这样就保证了数据访问周期发生的存储访问失效状态信息不会被指令预取周期发生的存储访问失效破坏。

存储器相关文章:存储器原理

评论