采用创新降耗技术应对FPGA静态和动态功耗的挑战

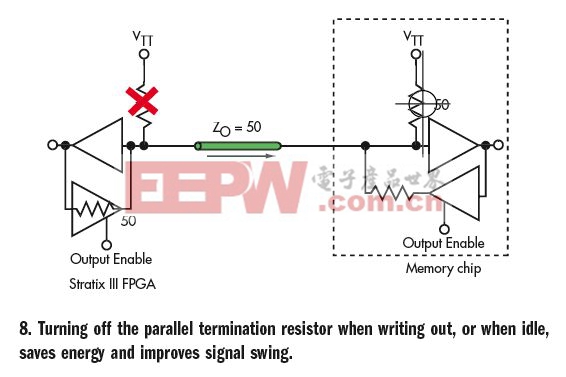

通过支持动态片上终止,根据执行的是读还是写操作,FPGA设计师可将并接终止电阻置为“通”或“断”(开路)状态。在写存储器时,FPGA输出驱动器阻抗必须匹配传输线。但,连至VTT的并接电阻既耗电又减低了信号摆幅。为避免这种情况,可将该电阻关断(图8)。

在读存储器时,接通并接电阻以终止传输线以便减少恶化信号完整性及影响可靠读取数据能力的反射。

当总线无论执行来自FPGA的写操作还是空闲时,都将显著体现动态片上终止的好处。首先,功耗得以极大降低——在一个72位的DDR2总线上,可降低1.6 W的静态功耗。另外,当写操作时,可获得一个纯粹的串接线终止。最后,它不再需要大量的板上终止电阻,从而降低了板成本和复杂性。

因DDR3工作在1.5 V(DDR2是1.8 V),所以,DDR3比DDR2省电30%以上。例如,一个带72脚、具有片上终止的200MHz或400Mbit/s存储器仅一个接口的功耗就是3.9W。采用动态片上终止(其中,在执行写或空闲时,并行终止电阻关断)可降耗1.6 W。若同时采用DDR3和动态片上终止,功耗将降至1.6W,从而一共节省了2.3W。这些数据是仅就一个接口来说的(也即,FPGA中的4个存储器接口共将省电9.2W)。

向极小的65nm及更精微工艺节点的迈进,能带来摩尔定律所预期的密度和性能方面的好处。但,性能的提升导致功耗的巨大增加,从而带来将耗费不可承受功耗的风险。

若不采用降耗措施,静态功耗将显著增加。另外,若没有专门的功耗优化举措,动态功耗将随着逻辑容量的增加和开关频率的升高而增加。

以能力非凡并具创新的架构结合工艺技术和电路技巧方面的进步可应对这些功耗挑战,它们为当今基于FPGA的日益复杂的设计提供了一个有效和可升级的方案。

评论