采用创新降耗技术应对FPGA静态和动态功耗的挑战

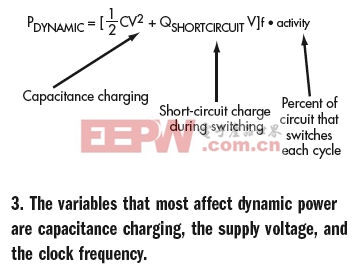

借助工艺节点的不断缩微带来的减小电容和降低电压的好处,动态功耗的降低遵从摩尔定律。挑战在于,伴随每一工艺节点的缩微以及最高时钟频率的增加所引发的问题。虽然就相同的电路来说,其功耗随每一工艺节点的缩微在一直下降,但同时FPGA的容量在翻番,且最高时钟频率也在不断增加。

FPGA架构

在架构、工艺技术和电路技术方面的进步有助于解决这些功耗挑战。Altera的Stratix III FPGA就是这样一种产品。

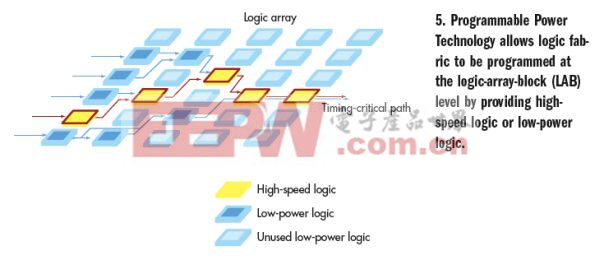

Altera的可编程电源技术(Programmable Power Technology)有助于降低高端FPGA的功耗。传统上,所有高性能的FPGA都由高性能的建构实现,其中,每一逻辑单元(LE)都以大的漏电功耗为代价来提供最佳性能。

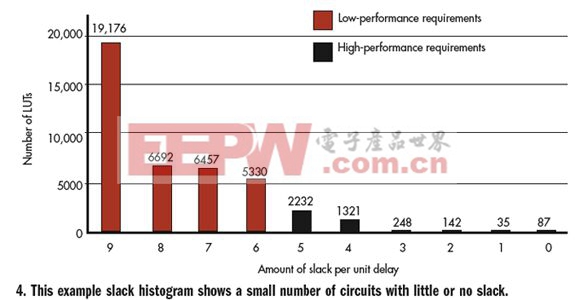

可编程电源技术利用如下事实:设计中的许多电路具有剩余能力,所以并不需要最高性能的逻辑。图4显示的是一个典型的剩余能力柱状图,其中,大多路径(左侧)具有剩余,只有不多的关键路径(右侧)需要最高性能的逻辑以满足时序要求。

采用可编程电源技术,根据特定逻辑路径所需的是高速还是低速逻辑,通过提供高速或低速逻辑的方法,可对Stratix III的逻辑构造在逻辑阵列块(LAB)级进行编程(图5)。基于这种思路,选出所占比例很小的对时序有苛刻要求的电路进行高速设定,而剩下的实行低功耗设定,采用这种方法,可将低功耗逻辑的漏电功耗降低70%。将不使用的逻辑、以及DSP块和TriMatrix存储器设定为低功耗模式将进一步降低功耗。

评论