采用创新降耗技术应对FPGA静态和动态功耗的挑战

可选核电压

可选核电压允许设计师根据性能需求采用0.9或1.1V核电压。0.9V核电压提供整体上最低的动态和漏电功耗;而1.1V核电压提供整体上的最高性能。动态功耗与核电压的平方成正比,而静态功耗是核电压的2.5次方。

在板卡设计时,可选核电压输入可被设定为0.9 V或1.1 V。该核电压为核构造内的所有LAB、存储器和DSP功能提供工作电源。可选核电压影响构造性能,所以,若在软件中选择了器件和速度等级,则还需进行核电压选择。该软件利用与所选核电压相对应的时序和功耗模型来实现全部依赖时序和依赖功耗的分析和优化。

当选择采用哪种核电压时,设计师必须考虑由时序分析得出的系统性能需求。若采用0.9 V就能满足系统性能要求,则肯定比采用1.1 V所用的功耗低。

技术融合

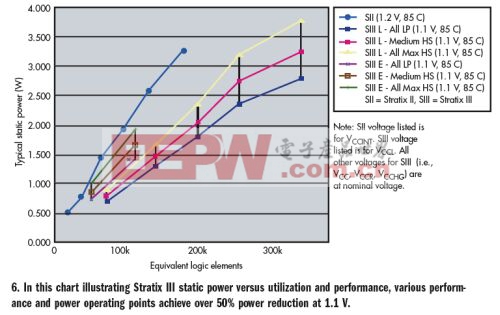

在1.1 V,将可编程电源技术和可选核电压结合起来,可提供降耗50%以上的各种性能和功耗工作点(图6)。基于所用的各种资源(如:DSP块和TriMatrix存储器块),静态功耗会显著不同。

根据核电压和高速逻辑与低功耗逻辑比例的不同,总合起来的静态和动态功耗也各异。在许多设计中,当不需要FPGA的最高性能时,可将设计的整体功耗降低50%以上。

工艺和电路技术

半导体行业通过在设备、工艺技术、设计工具和电路技术方面的巨大投入一直在不懈地迎击随着工艺尺度的缩微所带来的不断挑战。特别是业界面对的随着工艺尺度的缩微而不断增加的漏电流问题。因此,采用了在65nm(及更精微)工艺节点许多广为人知的技术在保证或提升性能的同时来管理漏电功耗,这些技术有:铜布线、低k电介质、多阀值晶体管、可变栅长晶体管、三闸级氧化层、超薄栅氧化层、应变硅。

评论