蓝牙HCI-UART主控制接口的FPGA设计与实现

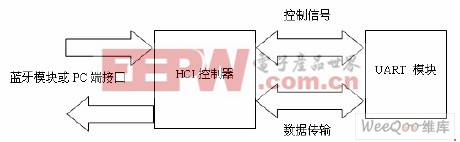

主机与蓝牙模块之间使用指令——应答的方式进行通信,主机向主机控制器发送指令分组,主机控制器执行某一指令后,大多数情况下会返回给主机一个指令完成事件分组,该分组携带有指令完成的信息。如果指令分组参数有误,返回的指令状态事件分组就会给出相应的错误代码。主机与主机控制器间的数据交换则通过数据分组实现。主控制器系统原理框图如图2 所示。

图2

3.1 UART 的设计

UART 的设计主要包括三个部分:发送器、接收器和波特率发生器,设计采用分模块完成[10]。

(1)波特率发生器:

UART 的数据接收和发送是通过对波特率的设置进行实现的。波特率发生器采 用分频器实现,分频得到一个频率为波特率16 倍的波特率时钟clk_baud,分频数N 计算公式如(1)所示, 其中clk_sys 表示系统时钟,baudrate 为UART 的波特率。

(2)发送器模块:

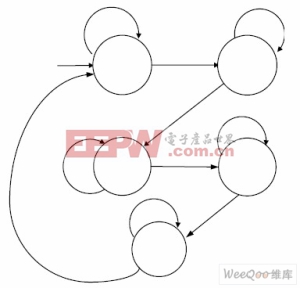

检测到发送信号时,装载数据,根据数据产生奇偶校验位,按通信协议帧的格式的要求依次发送起始位、数据位、奇偶校验位和停止位,并产生各种控制信号。整个发送过程采用有限状态机实现,分成五个状态(空闲idle,发送起始位send_start,发送数据send_data,发送奇偶校验位 send_parity,发送停止位send_stop),具体过程如图3 所示。

图3 发送器状态图

评论