一种基于FPGA的CAN总线通信接口的设计

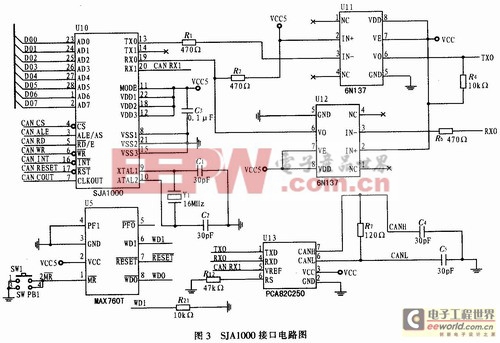

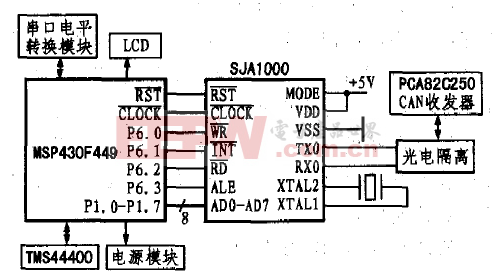

1.2 CAN总线接口电路

选用Philips公司的SJA1000作为CAN控制器,采用PCA82C250作为CAN收发器,并在CAN控制器与收发器之间使用6N137进行光电隔离,以增强抗干扰能力。将MODE引脚接高电平即SJA1000工作在INTEL模式,引脚与复位芯片MAX706T的RESET引脚相连,进行全局复位。在FPGA与SJA1000连接时需要使用741V164245电平转换器完成CAN总线5 V TTL电平向3.3 V FPGA I/O电平的转换。另外,SJA1000的RX1引脚与PCA-82C 250的VREF引脚相连,使用输入比较器旁路功能,可减少内部延时,增加正常通信的总线长度。具体的接口电路如图3所示。

2 FPGA逻辑控制程序

2.1 SJA1000逻辑控制

由于SJA1000地址线与数据总线复用,FPGA不仅仅要产生SJA1000读写控制引脚的信号逻辑,还需要模拟单片机等处理器产生对SJA1000的寻址信号,实际上是一个向SJA1000写地址的过程。根据SJA1000技术手册的时序要求,要完成对SJA1000内寄存器的正确读写,接口逻辑必须在地址锁存信号ALE为高电平时将SJA1000的寄存器地址当作数据写入,然后在ALE和片选信号![]() 为低电平后使能SJA1000的读写控制信号(WR或RD)。SJA1000的逻辑控制采用状态机的方式完成,状态机流程图如图4所示。起始态为IDLE态,当接收到数据读写等命令时,进入ADDR-ESS态,向SJA1000写入相应寄存器的地址值。然后根据命令类型决定下一个态是写寄存器状态(WR1~WR3)还是读寄存器状态(RD1~RD4)。以写寄存器为例,在WR1态ALE、

为低电平后使能SJA1000的读写控制信号(WR或RD)。SJA1000的逻辑控制采用状态机的方式完成,状态机流程图如图4所示。起始态为IDLE态,当接收到数据读写等命令时,进入ADDR-ESS态,向SJA1000写入相应寄存器的地址值。然后根据命令类型决定下一个态是写寄存器状态(WR1~WR3)还是读寄存器状态(RD1~RD4)。以写寄存器为例,在WR1态ALE、![]() 、

、![]() 等信号置为非有效态。将

等信号置为非有效态。将![]() 置为有效状态;在WR2态ALE、

置为有效状态;在WR2态ALE、![]() 为非有效态.而将

为非有效态.而将![]() 信号置为有效态,在时钟的下降沿将数据写入寄存器。WR3状态保持

信号置为有效态,在时钟的下降沿将数据写入寄存器。WR3状态保持![]() 有效,WR信号变为无效,进入IDLE态,一次写周期完成。

有效,WR信号变为无效,进入IDLE态,一次写周期完成。

评论