基于LPC2119的CAN总线智能节点的设计

引言

微控制器与can总线连接的传统方式是将cpu与总线控制器和总线收发器相连后再接入总线网络,这样使cpu外围电路复杂化,整个系统受外部影响较大。为了解决这一问题,很多单片机厂商纷纷将can控制器集成在单片机芯片上。目前,单片机内部集成的can控制器有motorola公司的mc68hc912dg128a、philips公司的p87c591和arm7

lpc2xxx系列、atmel公司的at89c51cc01和at89c51cc02、intel公司的tn87c196ca和tn87c196cb以及cygnal公司的c8051f040等。

lpc2119是philips公司推出的一款性价比很高的arm7核处理器,内部集成两路独立的can控制器。arm核的处理器具有性能高、成本低和能耗小的特点,适用于多种领域,如嵌入式控制、消费/教育类多媒体、dsp和移动式应用等。本文主要介绍lpc2119的can总线智能节点的设计。

硬件设计

lpc2119处理器特点

lpc2119是基于一个支持实时仿真和跟踪的16/32位arm7tdmi-stm cpu,并带有128 kb嵌入的高速flash存储器。128位宽度的存储器接口和独特的加速结构使32位代码能够在最大时钟速率下运行。对代码规模有严格控制的应用可使用16位thumb模式将代码规模降低超过30%,而性能的损失却很小。实行流水线作业,提供embedded ice逻辑,支持片上断点和调试点,具有先进的软件开发和调试环境。 lpc2119具有非常小的64脚封装、极低的功耗、多个32位定时器、4路10位adc、2路can、pwm通道、多个串行接口,包括2个16c550工业标准uart、高速i2c接口(400 khz)和2个spi接口,46个gpio以及多达9个外部中断,特别适用于汽车、工业控制应用以及医疗系统和容错维护总线。

lpc2119内部集成2个can控制器,每一个can控制器都与独立can控制器sja1000有着相似的寄存器结构。其主要的区别在于标识符接收过滤的编程操作上,篇幅有限,这里不作详述。它的主要特性有:单个总线上的数据传输速率高达1mb/s;32位寄存器和ram访问;兼容can2.0b,iso11898-1规范;全局验收滤波器可以识别所有的11位和29位标识符;验收滤波器为选择的标准标识符提供full can-style自动接收。

can智能节点硬件电路

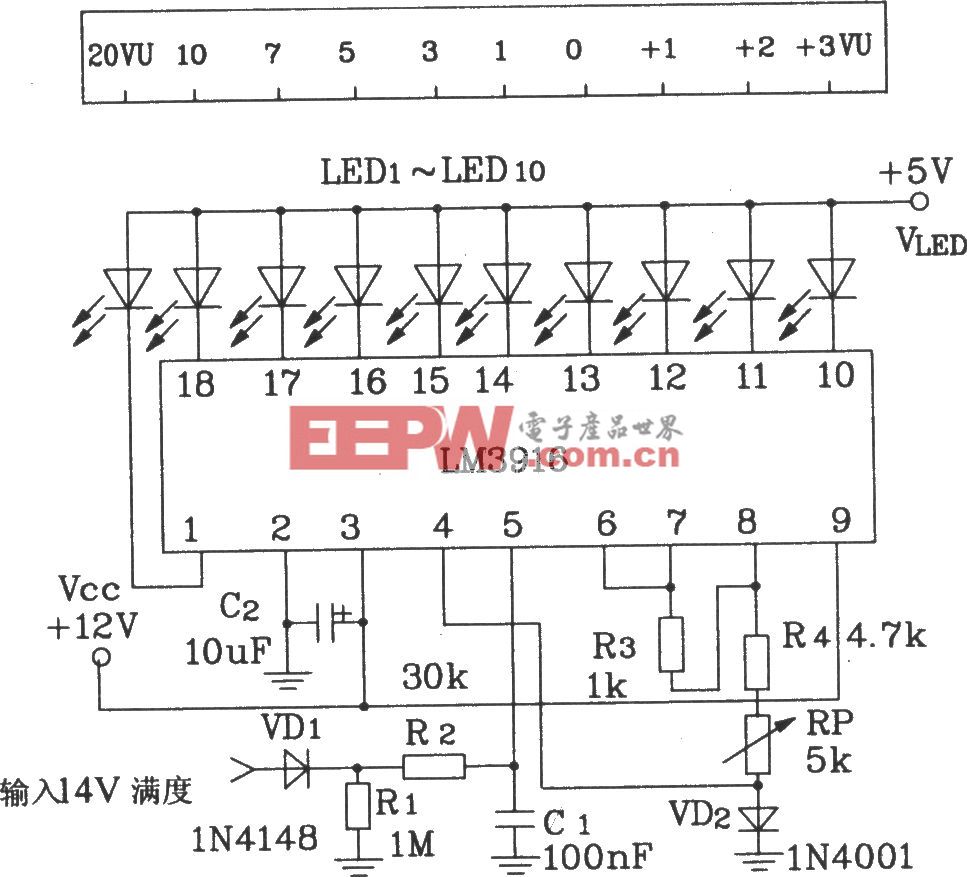

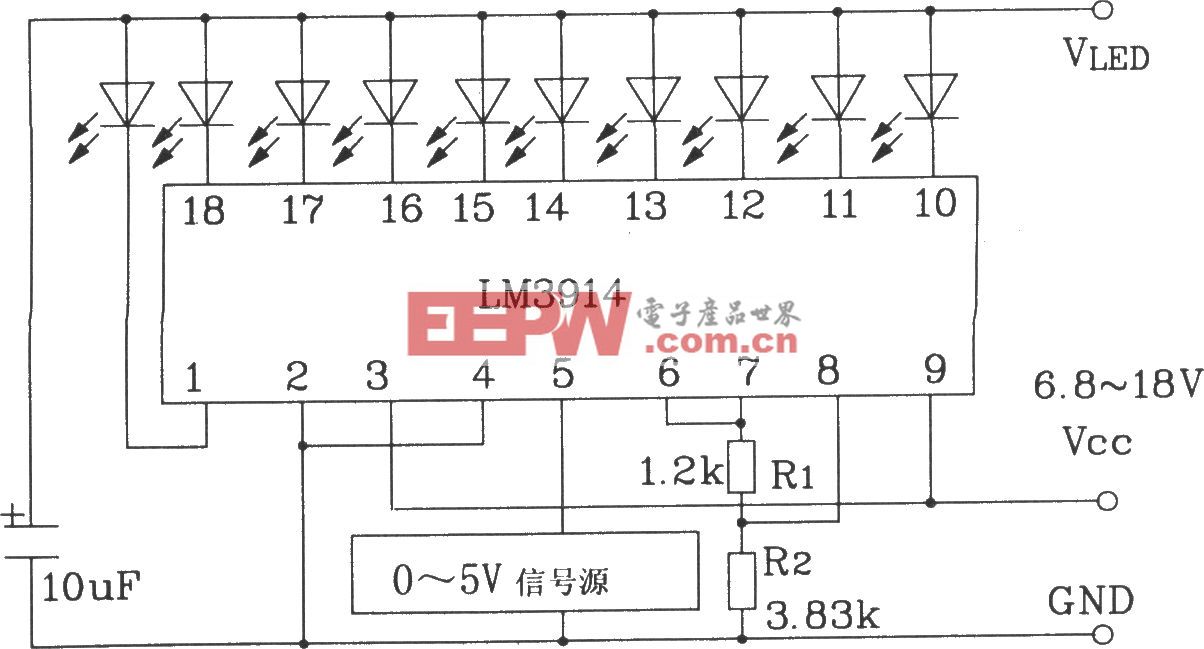

can接口部分包括lpc2119(内置can控制器)、光电耦合器和总线收发器,如图1所示。

can总线遵循iso的标准模型,分为数据链路层和物理层。在工程上通常由can控制器和收发器来实现。收发器选择philips公司的tja1050高速收发器,它符合iso11898 标准。can控制器主要完成can的通信协议,实现报文的装配和拆分、接收信息的过滤和校验等。收发器tja1050则是实现can控制器和通信线路的物理连接,提高can总线的驱动能力和可靠性。

为了进一步提高系统的抗干扰能力,lpc2119引脚tx1、rx1与收发器tja1050并不直接相连,而是通过高速光耦6n137后与tja1050相连。电路中采用隔离型dc/dc 模块向收发器电路供电。dc/dc 模块采用金升阳的b0505s-1w定电压输入隔离非稳压单输出型dc/dc模块,隔离电压≥1000vdc。这样就可以很好地实现总线上各接点的电气隔离,这部分电路虽增加了接点的复杂性,但却提高了接点的稳定性和安全性。

tja1050与can 总线的接口部分也采用了一定的安全和抗干扰措施。canh和canl与地之间并联两个小电容ch和cl可以滤除总线上的高频干扰并具备一定的防电磁辐射能力。电容值须由节点的数量和波特率决定,当tja1050 的输出级阻抗大约是20 ,总线系统有10 个节点速度是500kbit/s,则电容的值不应该超过470pf。另外在两根can 总线接入端与地之间分别反接了一个保护二极管。当can 总线有较高的负电压时,二极管的短路可起到一定的过压保护作用。根据tja1050的特性,本设计中can终端电阻使用了分裂终端,即总线端节点的两个终端电阻都被分成两个等值的电阻,用两个60 的电阻代替一个120 的电阻,这样可以有效的减少辐射。由于使用了分裂终端tja1050的emc,性能得到优化而且不会产生扼流。

软件设计

软件调试环境采用keil公司的keil uvision 3,通过ulink仿真调试。软件设计关键部分是编写can控制器(在lpc2119内部)的驱动程序。主程序只需通过调用驱动程序提供的接口来实现数据的接收和发送。can控制器驱动程序包括四部分内容:can控制器的初始化、报文的接收、报文的发送和总线异常处理。

lpc2119中can控制器的初始化

系统是否能正常地工作,初始化程序的设计是个关键。必须对写入每个寄存器的内容进行仔细和全面的考虑,否则系统将无法正常运行。can初始化主要是设置can的通信参数,即通过对can控制器中的寄存器进行设置,从而确定can控制器的工作方式等。lpc2119中can控制器的初始化与独立can控制器sja1000初始化过程相似。初始化can控制器的操作包括:硬件使能、配置管脚连接、软件复位、设置总线波特率、配置模式寄存器、配置中断工作方式、配置验收滤波器工作方式、启动can等。设置总线波特率是个难点,所有can节点的波特率要相同才能正常工作,要注意正确配置vpbdiv和pll寄存器。

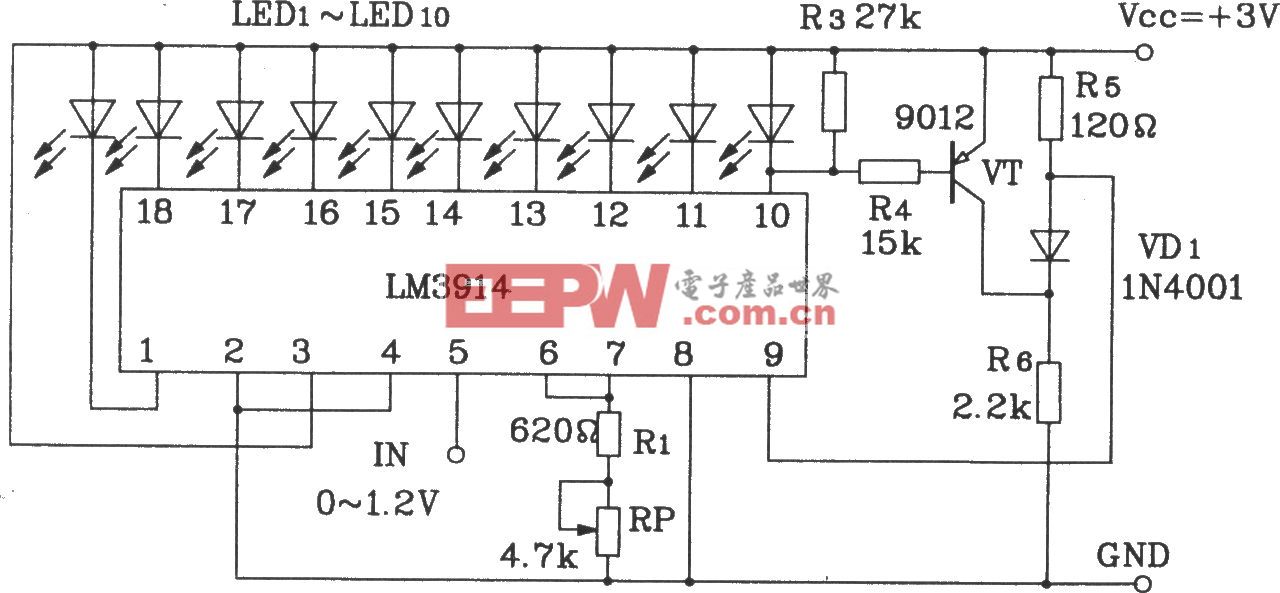

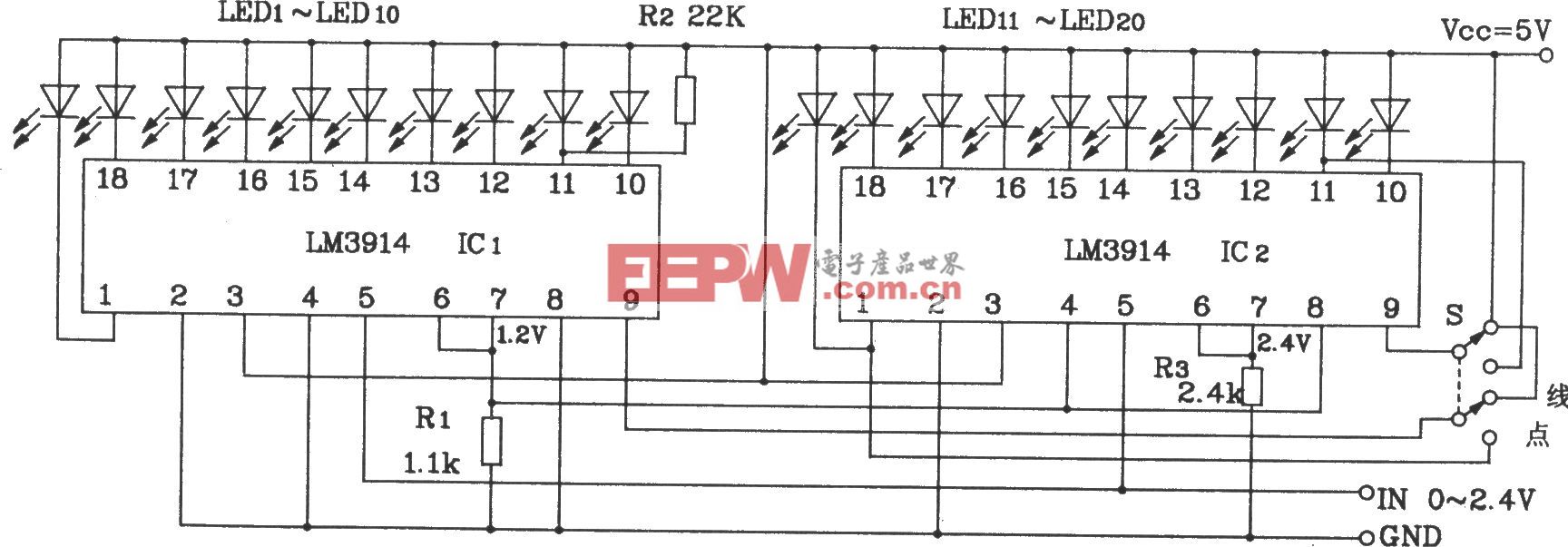

can报文的接收

can报文的接收采用中断方式。在arm7tdmi核处理器中向量中断控制器(vic)具有32个中断请求输入,可将其编程分为3类:fiq、向量irq和非向量irq。lpc2119芯片具有24个中断源,每个片内外设都有一条中断线连接到向量中断控制器, 其中can控制器的vic通道号是19-23。考虑到can控制器的中断源较多,笔者采用非向量中断。

为了避免接收到的数据因为没有得到及时处理而造成数据丢失,笔者定义了接收缓冲区,采用环形缓冲结构(类似于sja1000can控制器中64字节fifo环形缓冲)来接收数据。结合定义的环行缓冲区来进行can报文的接收程序设计。can报文接收的程序流程如图2所示。

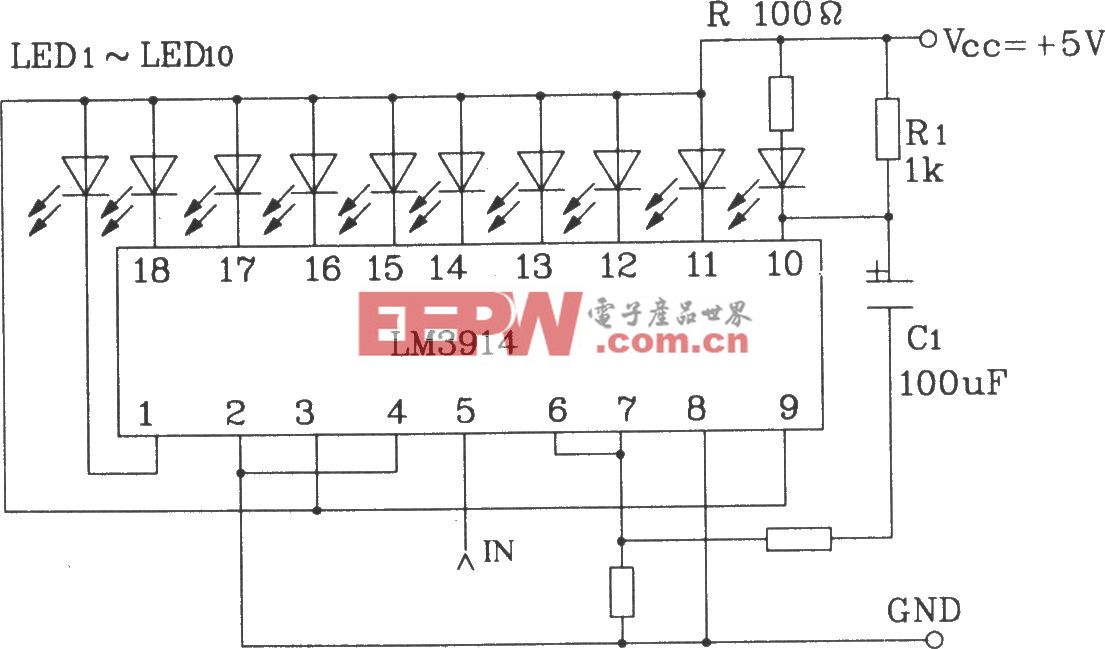

can报文的发送

lpc2119中can控制器为了提高大量数据发送的效率,每个can控制器配有三个独立的发送缓冲寄存器,这点和sja1000有所不同。因此与sja1000的发送程序相比要相对复杂。因为发送时是根据缓冲区的实际情况有选择的把数据写入三个发送缓冲之一。每个缓冲区的状态通过查询cansr得知。所以在设计发送程序的时候要先判断哪个缓冲是空闲的,然后在把数据写进缓冲区,启动发送。can报文发送程序流程如图3所示。

can总线异常处理中断程序

can控制器根据can2.0规范来对can总线上发生的错误进行处理。

在总线发生严重故障的情况下,can节点有可能脱离总线,此时以下寄存器被置位:cansr的bs位、canir的bei和ei位以及canmod的rm位。软件下一步必须置零rm位。发送错误计数器将递减计数(11个连续的隐性位)的第128个事件,总线释放条件软件可通过读取tx错误计数器对计数器递减计数的情况进行监测。其它一些不是很严重的错误一般不会引起总线错误,即使不处理也不会产生什么致命错误,如果为了提高中断处理速度,可根据实际情况裁剪中断服务程序。

结束语

本设计采用arm7tdmi内核的嵌入式微控制器作为节点的主控cpu,其丰富的片内资源,特别是内嵌can控制器简化了节点的硬件电路。对比与sja1000的异同点本文详细分析了can控制器的软件设计方法。该设计作为can总线节点的一个模块,能够和仪器仪表等设备相结合,使其具有网络通信的能力,有着广阔的应用前景。

评论