一种因光纤漂移引起SERDES FIFO溢出的解决方案

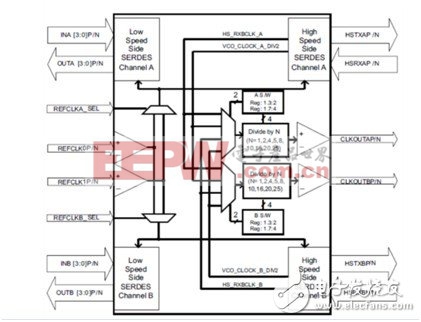

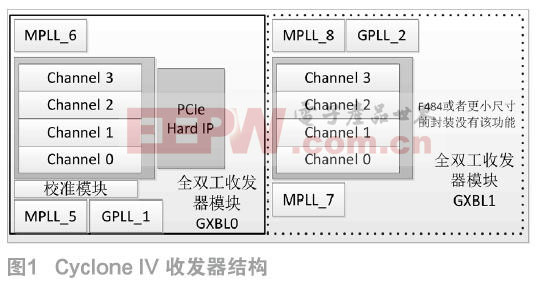

高速侧 SERDES 的 CDR 主要用于从输入串行数据中恢复时钟信号,恢复的时钟信号从CLKOUTAP/N 和 CLKOUTBP/N 输出。输出信号频率有多种选择:通过寄存器配置,用恢复时钟频率除以 1, 2, 4, 5, 8, 10, 16, 20, 或者 25 均可。

对于每个通道而言,高速侧 SERDES 和低速侧 SERDES 可以工作在一个时钟域,即两者使用同一参考时钟;同时,TLK10002 也提供了另外一种时钟模式,即高速侧 SERDES 和低速侧SERDES 使用不同的参考时钟,这种情况下,高速侧锁相环和低速侧锁相环会工作在不同的时钟域。

图 2 TLK10002 内部时钟架构

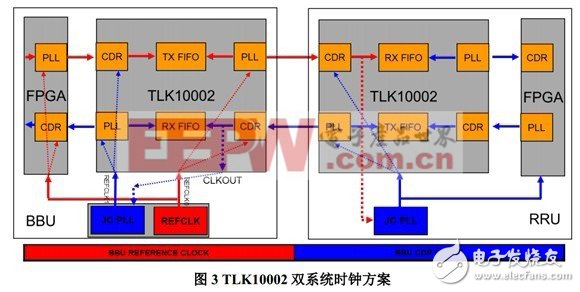

2.2 TLK10002 双时钟系统方案

基于双时钟 TLK10002 构建的系统级联方案如图 3 所示。在这种方案中,TLK10002 高速侧SERDES 和低速侧 SERDES 采用不同的参考时钟。

在 BBU 一侧,高速侧锁相环采用本地的参考时钟,一旦高速侧锁相环锁定,并且 BBU 和 RRU 之间建立稳定的链路,BBU 一侧 TLK10002 的 CDR 会有稳定输出,这个输出给 BBU 上的 Jitter Cleaner 提供参考输入。 一旦 Jitter Cleaner 正常锁定,它的输出又会作为低速侧锁相环的参考输入。

采用这种配置,由于 SERDES 本身可以处理最高 200ppm 的频率偏移,发射和接收通道的速率是完全相互独立的。这样,FIFO 的两侧完全工作在同一时钟域,FIFO 就不会存在溢出的风险。在这种情况下,FIFO 仅仅用来吸收不同时钟之间的相位偏移和补偿 jitter cleaner 的跟踪能力。

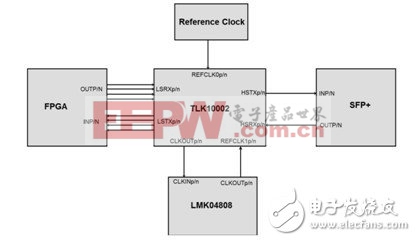

2.3 双系统时钟方案的具体实现

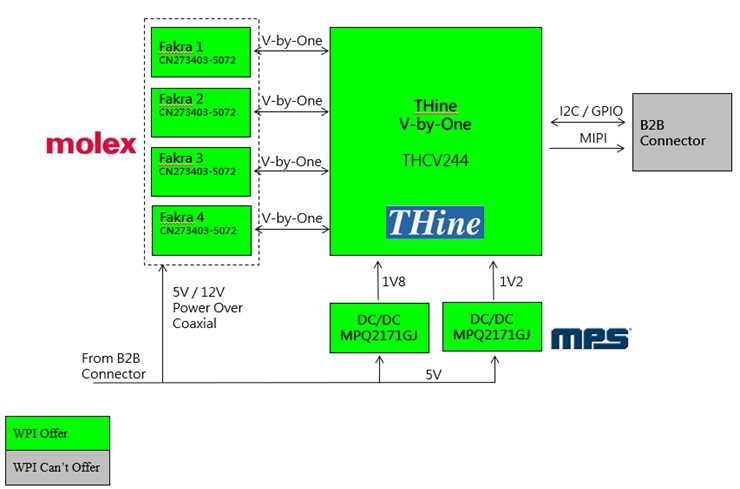

以 BBU 一侧为例,双系统时钟方案具体实现方式如下图 4 所示。在这个方案中,由于 LMK04808具有超低相位噪声特性,我们使用它作为抖动消除器。

图 4 采用双时钟方案构建 BBU SERDES 系统

对图 4 所示的系统,系统配置及操作顺序如下:

1) 正常配置 TLK10002 0X00 到 0X0D 寄存器。

2) 等待 TLK10002 高速侧锁相环 HS PLL 正常锁定。//只要本地参考时钟准备就绪,高速侧锁相环即可锁定(此时并不需要建立稳定的 10G 链路)。

3) 切换 TLK10002 ENRX:先置为 0,再置为 1。//使 HS SERDES 自适应链路状况。

4) 等待 10ms。 //等待 HS SERDES 设置参数,确保 CDR 为 LMK04808 提供有效的参考时钟。

评论