一文通解基于VLT技术的新型DRAM内存单元

VLT内存单元

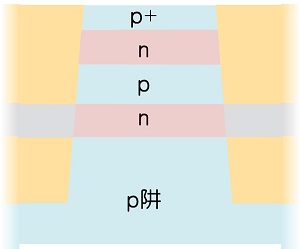

本文引用地址:https://www.eepw.com.cn/article/201701/342389.htmKilopasss的全新内存单元基于一种垂直分布的闸流体(也被称为半导体控制整流器,或SCR)。这种采取pnpn结构的堆栈建构于一个p-阱上,可带走来自底部n型层的任何空洞。

图6:VLT内存单元:带有写入辅助的PMOS晶体管的闸流体

在浅沟槽隔离(STI)结构中植入一个埋入式字符线,使底部的n层连接到一个字符。埋入式字符线与外部铜金属M1层字符线透过具有较大电阻的金属钨实现连接,因而可以制造比传统DRAM更长的字符线。

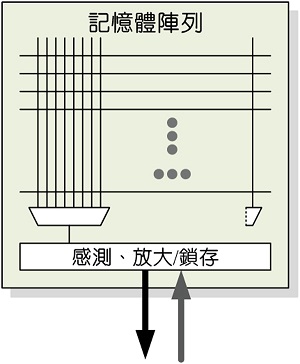

由于感测机制并非采用电荷分配,使感测放大器可承受更长的位线。因此,这种技术可以支持高达2Kbit宽、4Kbit深或总共8M位的MAT——远大于传统的DRAM MAT。采用更少片较大型MAT拼接成的内存芯片较采用多片小尺寸MAT的花费更低,因而可使VLT内存的数组效率达到77%,相形之下,同样采用2x-nm节点的传统DRAM效率只有64%。

以VLT内存单元打造LPDDR4内存

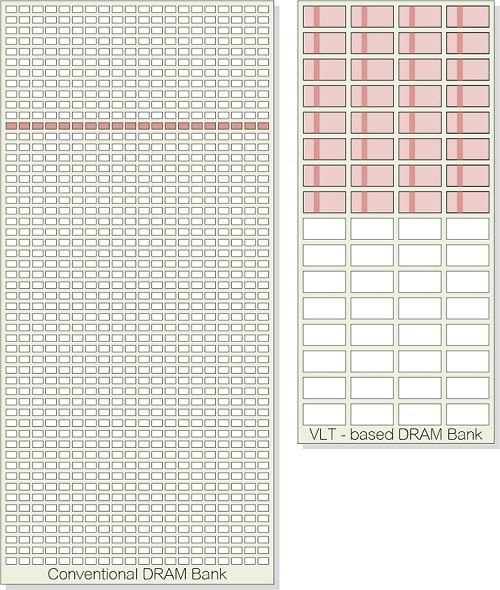

MAT容量增大后,LPDDR4内存组就可以用更少的MAT组成。单纯按照位数计算,基于VLT技术的内存组将包含64个MAT,相形之下,传统DRAM的内存组需要配置848个更小的MAT。不过,接下来的问题就是如何最有效配置这些MAT。

一种配置方式是每个MAT都带有512个支持4K位线的感测放大器,这意味着每个感测放大器都有多任务器用于在8条位线中进行选择。其中,多任务器的选择基于CAS地址;进一步针对图3的内存数组进行修改后,新的原理图如下:

图7:为VLT内存添加位线多任务器

因此,对于每个被选定的分页,每个MAT中只有八分之一的位线会被选择,这与普通DRAM实现方式中所有位线都被选中的情况不同。但在传统DRAM中并不可能实现这种更高效率的感测放大器使用方式,因为所有的位线都必须被读取,以实现回写的目的。由于VLT读取并不是破坏性的,因而无需回写操作,且多个内存单元可共享感测放大器。

另一个问题是如何在一个MAT实体数组中配置这些MAT。基于VLT MAT的灵活性,实体上配置这些MAT可以不必与逻辑上的配置完全吻合。只要妥善安排各总线的路径,任何形式的配置都是可能的。举例来说,一个内存组可被配置为4×16个MAT数组,同时传输理论上与传统LPDDR4相同的数据。

图8说明传统DRAM和VLT技术在内存分页选择上有什么不同:传统DRAM选择一行中的所有MAT,而VLT则从中选择了一个4×8的MAT区块。

图8:内存分页选择,其中被选定的MAT是红色的。传统DRAM透过行来选择分页,而VLT DRAM则以单元区块选择分页。

由VLT制造的LPDDR4,在外部操作上与传统LPDDR4完全相同。内部操作可能有所差异,例如不必再回写和预充电,但这并不会影响DDR控制器;如果满足了VLT的时序要求,其内存的逻辑组织方式与传统DDR完全一致。

免除刷新

VLT内存单元最明显的优点之一就是不需要刷新。不过,刷新已经成为DRAM作业的一部份了;无论内存处于闲置状态或是被接通,都必须进行刷新操作,以避免数据丢失。

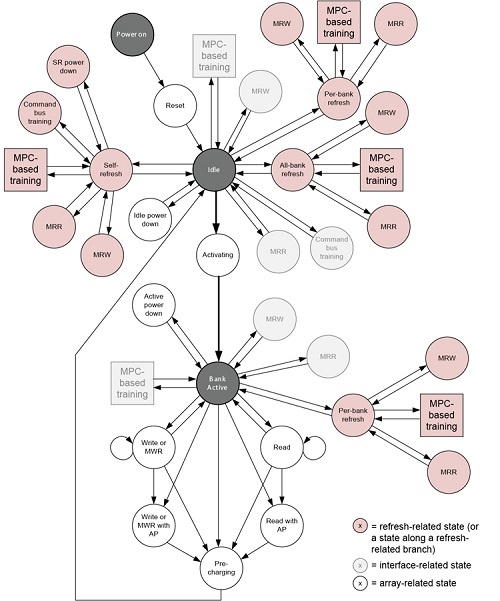

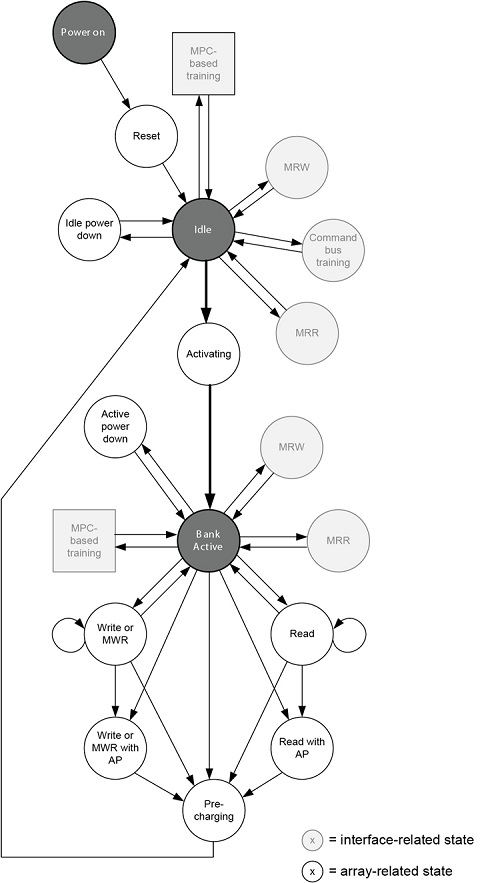

完整的DDR控制器状态机说明了刷新对于运作的影响,如图9所示,所有红色的状态都与刷新或者基于刷新的分支相关;而使用了VLT技术,这些状态都是冗余的,而且能够被消除。

图9:传统DRAM建置的LPDDR4状态原理图,与刷新有关的状态以及与基于刷新的有关分支状态都被标注为红色,标注为灰色的状态则与接口相关。

图10则是一种简化的状态机,其中与刷新有关的状态都已经移除了。在设计基于VLT的内存时,设计者可以选择现有的DDR控制器,因应那些不需要的状态加以调整;也可以设计优化的DDR控制器,省去所有与刷新相关的电路——这种方法将占用更小的芯片面积,以及降低功耗。无论选择哪一种控制器,都不会影响其他系统与内存芯片的互动。

图10:移除与刷新相关状态后的LPDDR4状态原理图

结语

VLT内存单元可以打造一种比普通DRAM内存单元成本更少、功耗更低的内存,目前VLT内存芯片已能与现有的LPDDR4内存完全兼容了。透过适当设计架构、命令以及时序,VLT内存芯片就能与传统内存芯片无差别地应用在实际系统上。

基于VLT的内存数组采用一个可在内部作业处理差异的接口,使其得以与标准的LPDDR4控制器配合使用。换句话说,设计一款免刷新的LPDDR4控制器,使其仍具备完整的控制器功能以支持外部接口,并确保现有驱动器都能继续正常作业,而只是在内部忽略与刷新有关的操作,将有助于大幅节省成本,以及降低功耗。

评论