微型电感器的简化模式设计

表上部为设计输入参数,下部为输出

符号 | 名称 | 数值 |

|---|---|---|

技术条件 | ||

f | 频率 | 5MHz |

IDC | 输出电流 | 1A |

△IPP | 电流脉动 | 3A |

Uin | 输入电压 | 40V |

Uo | 输出电压 | 5V |

材料数据与技术参数 | ||

N | 磁心叠层数 | 12 |

hsmax | 磁心最大允许高度 | 16μm |

Bsat | 饱和磁通密度 | 1.1T |

ρc | 导体(Cu)的电阻率 | 2μΩ-cm |

ρs | 铁心(80%NiFe)的电阻率 | 20μΩ-cm |

hsep | 纵向分隔铁心 | 15μm |

Wcon | 与铁心接触宽度 | 40μm |

Sres | 光刻胶凸条的斜度 | 5.5 |

器件参数 | ||

L | 需要的电感值 | 292nH |

μr | 设计要求的磁导率 | 490 |

D | 转换器的占空比 | 12.5% |

hs | 磁心总高度 | 12.0μm |

δs | 在5MHz时磁心的穿透深度 | 2.25μm |

Ws | 磁心的长度(参见图1) | 9.2mm |

BPK | 磁通密度波动值 | 0.66T |

σ | 电流密度 | 3.75A/m2 |

St | 每匝线圈的间隔宽度 | 76μm |

Wt | 每匝线圈的等效宽度 | 266μm |

hc | 导体高度 | 54μm |

δc | 在5MHz下导体的穿透深度 | 32μm |

SLat | 靠近磁心的横向宽度 | 534μm |

n | 匝数 | 3 |

Kend | 端匝损耗电阻因子 | 1.29 |

Ks | 由端匝引起的长度因子 | 1.22 |

Kc | 由St和SLat引起的宽度因子 | 2.62 |

计算性能 | ||

isat | 使磁心饱和的电流 | 2.5A |

RDC | 设计的DC电阻 | 101mΩ |

Fr | 设计在5MHz下的交流电阻因子 | 1.05 |

Kwind | 即Pwind=KwindRDCI2DC | 1.82 |

Pwind | 设计绕组中的总损耗 | 183mW |

Kcore | 谐波磁心损耗因子 | 3.62 |

Pcore | 设计磁心中的总损耗 | 136mW |

Wstot | 器件总长度 | 11.2mm |

2Wc.tot | 器件总宽度 | 4.2mm |

| 输出功率 | 5.0W |

| 功率密度 | 10.6W/cm2 |

η | 设计的效率 | 94.0% |

表1中的参数是假设的一个例子。

在上述的最佳设计中,磁心和绕组之间的分布功率损耗,即Pcoreloss/Pwind1oss=2/3。一般来说,只要忽略磁滞损耗,磁心叠层薄到和穿透深度可以相比,电感要求可用调节磁导率来满足的话,则图1构造的平面电感器和变压器,所有的优化设计将保持这个比例。

4电感调整

满足电感要求的一种方法是调整磁心的磁导率,这就产生了一个有利的磁场构造,避免了优化过程中引入的电感抑制。

对优化设计,为了获得要求的电感,需要有效的磁导率

式中σopt(η)是单位导体宽度,在效率为η时的电流密度。对于一个优化设计来说,一旦选定效率η,就完全指定了磁导率μr。

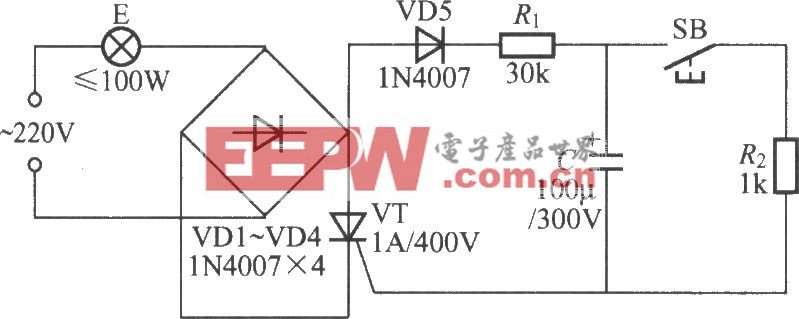

例如,假设表1中的参数,忽略了端匝和其他“无效”间距,以95.5%η98.5%范围设计,则相对磁导率的数值可能在100μr400范围内,如图3所示。对于某一个确定的效率,实际设计一般需要比图3中所示的磁导率要高,这是因为靠近磁心的间距和绝缘匝的间距,在简化模式分析中被忽略了,所以,增加了磁路的长度(见图1)。电感中电流的波形如图4所示。

图2叠层数N=12的功率密度与功耗百分数的关系曲线。二座标轴均用对数值,参数已在表1中假设。

图3给定叠层数N=12时的磁导体与功耗百分数的关系曲线。二座标轴均用对数值,参数已在表1中假设,忽略了端匝和其他“无效”区

评论