JPEG解码器IP核的设计与实现

1.6 IDCT模块设计

2D-IDCT的实现选用行列分解法,所以主要功能模块包括1D-IDCT模块和行列转置模块。因为全流水线实现系统解码硬件成本很高,所以设计中主要通过提高运算并行度和在功能模块内部实现流水线运算来提高解码速度。IDCT模块设计中采用了两个1D-IDCT处理单元,并通过流水线技术实现高运算速率。

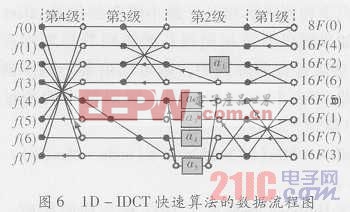

1.6.1 1D-IDCT模块设计

本设计采用了一种运算量少、数据流简单且适于流水线实现的IDCT算法。通过对1D-IDCT数据流程的合理划分,将其分4级,在每级中间插入寄存器,对每级流水线内部运算的时序进行合理安排,在每级流水线内共享算术单元,降低硬件成本。1D-IDCT快速算法的数据流程如图6所示。

本文引用地址:https://www.eepw.com.cn/article/162053.htm

本文引用地址:https://www.eepw.com.cn/article/162053.htm

通过对1D-IDCT数据流程的合理安排和资源共享,本设计共需4个加法器,4个减法器和4个乘法器,所用硬件资源比较少。而且本设计的处理速度快,每个时钟周期输入两个像素,完成1D-IDCT的延迟时间是6个时钟周期。在流水运算时计算一个8点1D-IDCT只需要4个时钟周期。

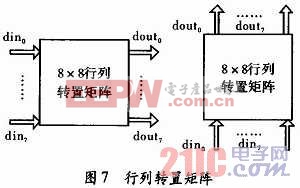

1.6.2 行列转置模块设计

行列转置矩阵的实现大部分设计采用双RAM进行乒乓操作完成,本设计采用一个8×8寄存器阵列和方向控制信号完成,可节省一半硬件资源,且控制简单。当有信号输入时,方向控制信号值初始设为0,这时寄存器阵列的输入输出方向是从左到右,64个时钟周期后方向控制信号反向变为1,这时寄存器阵列的输入输出方向是从下到上。如此循环,即可实现行列转置,如图7所示。

2 综合、仿真与性能分析

设计时先用Matlab进行算法级仿真与验证,在RLT级设计时采用Verilog语言实现,在Modelsim6.1中进行功能仿真,选择VIRTEX2系列xc2v250器件进行FPGA验证,从软硬件方面都验证了设计的正确性。

使用Synopsys公司的Design Compiler工具在0.18μm的SMIC CMOS工艺条件下,对RTL代码进行综合优化。通过设置不同的面积、时序及功耗约束条件,缩短关键路径的延时,时钟频率可达100 MHz的最优设计,综合出面积为721 695μm2,不包括存储单元需要34.6 kB标准门。本设计能每秒能够解码1 920×1 080图形25帧以上,所以也能用于一些有低成本需求的监控、录像系统。

3 结束语

介绍了基于静止图像压缩标准JPEG的解码器IP核的设计,描述了硬件设计过程,提出了一种高效、低成本的JPEG解码器架构。设计通过VIRTEX2平台进行了FPGA验证,并使用Synopsys公司的DC工具在SMIC 0.18 μmCMOS工艺条件下,对设计进行面积和时间的优化,在100 MHz时钟频率下工作时电路面积为721 695μm2,每秒能够解码1 920×1 080图形25帧以上。本设计还支持多种图像质量和图像格式,有较宽的压缩比范围,设计具有独立性和完整性,也适用于数码相机、手机和扫描仪等各种应用。

评论