JPEG解码器IP核的设计与实现

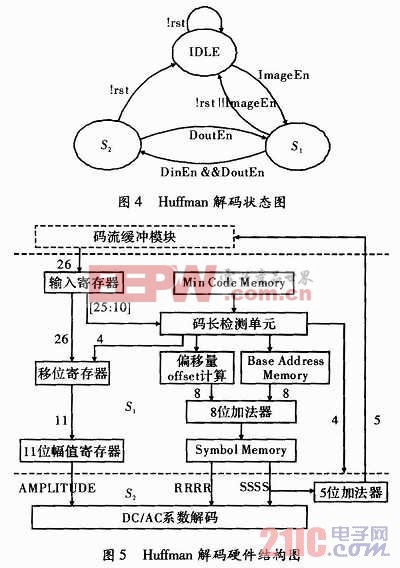

因为Huffman编码是无损压缩,不存在误差,所以Huffman解码出来的数据也是没有误差的。本设计采用一个简洁的Mealy型状态机实现,状态转移如图4所示。图5所示是相应的Huffman解码硬件结构图。本文引用地址:https://www.eepw.com.cn/article/162053.htm

接下来结合图4和图5介绍Huffman并行解码流程。

(1)初始化状态(IDLE):复位或图像压缩数据解码完成时进入的状态,初始化相关寄存器。

(2)解码状态1(S1):首先寄存从码流缓冲模块输入26位图像码流,将高16位输入码长检测单元,与Min Code Memory中存储的各长度最小码字并行比较,码长检测单元由选择器、比较器和一个16选4的选择器组成,得到码字的长度L。接着由码长为L的Huffman码与相应长度的最小码字Min(L)计算出偏移量offset,从Base Address Memory中取出最小码字Min(L)的地址Base Address,将两者输入8位加法器中,由式(1)可计算出该码字对应的解码符号地址。然后根据这个地址从Symbol Memory中取出解码符号,对DC来说是SSSS,对AC来说是RRRRSSSS。同时将移位寄存器中的码字左移L位,将高11位编码输入到幅值寄存器中。

(3)解码状态2(S2):将解析出的字长SSSS和码长L输入到5位加法器中,得出本次解码总位长,输出到码流缓冲模块,用于重新定位码流,更新输入数据。将幅值寄存器的高SSSS位选择输入一个12位中间寄存器的低位,该中间寄存器的高(12-SSSS)位移入幅值寄存器的最高位的相反值,若得到的中间寄存器的最高位为“1”,按.JPEG标准,要再加1。这样解析出来的就是频率系数,即DCT系数,对于DC来说就是差值DIFF。解析完幅值后,进行DC/AC系数解码。

DC/AC系数解码:计数器用于计算解析系数在块数据中的位置。若计数器值为零,表示解析出来的是DC系数的差值DIFF,要根据亮度色度选择信号选择相应DCk-1,根据DCk=DIFF+DCk-1计算出DC值,并且更新DCk-1。若计数器值不为零,表示解析出来的是AC值,接下来对应的有4个分支:1)若(RRRR,SSSS)=(0,0),表示此图像块解码结束,输出块解码结束标志DecOneBlock,并清零计数器;2)若(RRRR,SSSS)=(15,0),表示连续16个零系数,计数器加16,不输出;3)若SSSS不为零,且计数器值+RRRR=62,表示解析出来的是图像块的最后一个系数,计数器清零,并输出块解码结束标志DecOneBlock和DCT系数值;4)普通AC系数,计数器加1,输出计数器的值和DCT系数值。

1.4 反量化模块设计

本设计在Huffman解码后没有采用JPEG标准的先反Z字形重排再反量化的流程,而是先进行反量化操作。如此只要Huffman解码有DCT系数输出时才需要进行反量化运算,能减少无效操作,降低功耗。

反量化运算时先将相应的量化系数保存在寄存器阵列中,在Huffman解码模块有DCT系数输入时,按其地址取出相应的量化系数,相乘后输出到后级反Z字形重排模块。

1.5 反Z字形重排模块设计

根据模块输入数据的特点,提出了一种优化的硬件实现结构。因为一个8×8图像块经DCT变换后非零系数个数一般不超过总数据量的10%,所以设计中为寄存器阵列的每个寄存器都设定一个一位的使能标志,在初始化时先将寄存器阵列中寄存器和相应标志位都赋零值,在输入值为非零值时才写入相应地址,并置位对应的使能标志,这样在写入数据时不需要进行零数据的存储,而在输出数据时只要根据使能标志就能判断是要读寄存器阵列还是直接输出零,所以可以减少对存储器的读写操作,加快数据处理速度。

反Z字形重排模块不仅要接收反量化后的系数,对其进行反Z字形重排,同时要对图像块数据进行一次行列转置,这样可以节省2个寄存器阵列,降低硬件成本。为了提高运算并行度,提高解码速率,满足后级模块数据要求,反Z字形重排模块中采用了两个64×14位双端口寄存器阵列,进行乒乓操作。

评论