嵌入式系统中DRAM控制器的CPLD解决方案

DRAM存在着大量、复杂的时序要求,其中访问时间的选择、等待状态以及刷新方法是至关重要的。DRAM控制器必须正确响应80C186XL的所有总线周期,必须能将DRAM的部周期和其它访问周期分辨出来,其访问速度必须足够快,以避免不必要的等待周期。

在设计时,我们采用XC95C36-15 CPLD[2]以及4Mbits的V53C8258[3]DRAM作范例。15ns的CPLD,速度相对较高,价格比较便宜。用它设计成的DRAM控制器允许80C186XL的工作速度高达20MHz,并且XC95C36有异步时钟选择项。这种特性对本设计有很大的好处。

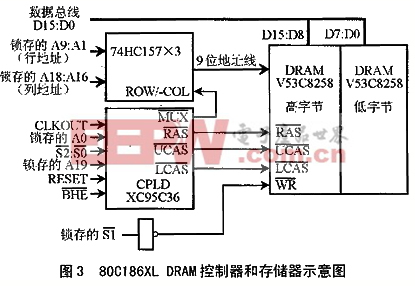

图3是80C186XL DRAM控制器和存储器的功能框图。

DRAM控制器由80C186XL状态信号S2、S1和S0的解码来检测总线的开始、类型和结束。这些状态线是在CLKOUT的上升沿开始有效,在CLKOUT的下降沿失效的。DRAM控制器发出的RAS和CAS信号应该在CLKOUT的下降沿同时有效,行列地址应该在CLKOUT上升沿附近提供。

DRAM控制器应该在CLKOUT的两个沿都应能正常操作。通过启用XC95C36的异步时钟选择项,每个XC95C36宏单元可以从可编程与阵列获得时钟。DRAM控制器使用80C186XL的CLKOUT信号作时钟输入。

DRAM控制器主要由两个相互联的状态机构成。这两个状态机,使得DRAM的控制与80C186XL是否进行等待状态无关。状态机A和地址多路控制信号(MUX)在CLKOUT的上升沿锁存。状态机B和RAS及CAS的逻辑在CLKOUT的下降沿锁存。DRAM控制器完整的VHDL语言的源代码可Email给cnhsx@sina.com索取。

DRAM控制器的状态图如图4所示,状态机A和B的起始条件分别是A0和B0。状态机A初始化DRAM控制器的序列,状态机B终止该序列。

在T2的下降沿,RAS逻辑采样状态机A的状态,锁存的地址线和总经状态信号。如果状态机A在A1状态(存储器读、写或刷新周期)并且总线周期为DRAM使用,则XC95C36插入RAS信号。

在T2的上升沿,状态机A也采样锁存的地址线。如果总线周期被DRAM占用,状态机A将从状态A1转移到A2,否则状态机A转换到A3。至此控制转移到状态机B。MUX逻辑采样RAS和BHE引脚的状态。如果RAS有效(指示DRAM在访问),并且总线周期下是刷新周期,XC95C36将插入MUX。MUX在行列地址之间切换,以便进行DRAM的读写操作。

在T3的下降沿,状态机B采样状态机A。如果状态机A处于状态A2(DRAM访问)或状态A3(存储器读或写,但不是DRAM访问),状态机B从状态B0转到B1。如果总线周期是一个DRAM访问周期,XC95C36继续保持RAS有效。CAS逻辑采样MUX的状态、锁存地址A0、BHE和总线周期状态。如果MUX有效(指示DRAM读或写),并且访问低字节,则XC95C36插入LCAS;如果MUX有效,并且微处理器访问高字节,XC95C36插入UCAS。DRAM读访问和DRAM刷新访问不同之处在于:对刷新来说,不需要MUX、UCAS和LCAS。

在T3的上升沿,状态机A等待状态机B中断此序列。如果MUX有效(DRAM读或写),它将保持有效。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论