基于FPGA的雷达数字脉冲压缩技术

FFT的每一级运算结束后,两块RAM功能互换,写使能变反,运算结束。RAM的每次输出数据需经过数据选择模块(datamux),该模块由地址产生模块输出的当前级数信号Stage控制。本系统采用三种FFT模式:1024点、512点和256点,均采用同一旋转因子ROM。根据FFT点数的不同,ROM的读地址expaddr做相应的调整,这样的设计也在很大程度上节省了芯片内的块RAM资源。

3 系统性能

针对本雷达信号处理机对实时性和高精度的要求,我们设计研制出具有自主知识产权的高性能脉冲压缩处理系统,该处理系统具有以下特点:

A 处理系统内部采用24位自定制浮点数据格式,能够兼顾处理系统的资源占用和处理精度。数据输入为定点数据格式,输出为标准32位浮点数据格式。

B 处理系统工作时,需要依次完成FFT运算、复数乘法运算和IFFT运算。在进行FFT和IFFT运算时,蝶形运算/乘法运算单元完成蝶形运算操作;在进行复数乘法运算时,该单元完成乘法操作。这两种操作在实际工程中分时实现,并且共享浮点数规格化处理硬件电路。

C 处理系统中进行FFT/IFFT运算的长度N(N=2048、1024或512)由雷达信号处理机的控制信号决定。

D 内置三组数据存储器(输入数据RAM、同址运算RAM、输出数据RAM),保证处理系统能全速运行,提高该处理系统的处理能力。

E 旋转因子(N=1024时的FFT运算旋转因子)以上电初值的形式存储在FPGA片内存储器中。当N=512、256时,其旋转因子从N=1024的旋转因子中抽取得到。N点IFFT的旋转因子由N点FFT的旋转因子取共扼得到。实验结果

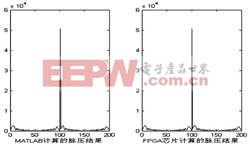

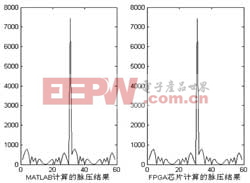

本雷达信号处理机存在三组时间—带宽指标,分别对其进行理论仿真和实际输出结果对照,其结果如图4、图5和图6所示。

本文引用地址:https://www.eepw.com.cn/article/151248.htm

图4 1024点脉冲压缩状态FPGA计算结果与MATLAB计算结果对比图

图5 512点脉冲压缩状态FPGA计算结果与MATLAB计算结果对比图

图6 256点脉冲压缩状态FPGA计算结果与MATLAB计算结果对比图

图4至图6分别对应时宽为60μs、20μs、6μs,带宽均为5M的线性调频信号。其中,左图对应MATLAB的计算结果,右图为FPGA芯片的输出结果。可以看到,FPGA芯片的输出结果和MATLAB仿真结果吻合。经测试验证结果良好,最大误差不超过-76db,在内部时钟频率80MHz条件下,完成1024点FFT 运行时间为146μs ,满足了雷达系统实时处理要求,达到了满意的效果。

评论