Intel、IBM 22/15nm制程部分关键制造技术前瞻

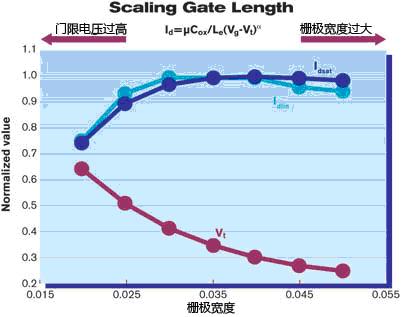

栅极宽度不断减小所带来的负面效应越来越明显。首先,为了消除短通道效应,人们不得不向沟道中掺杂磷,硼等杂质元素,这便导致管子门限电压Vt的上升,同时还降低了沟道中电子流动的速度,造成管子速度的下降。而且用来向沟道中掺杂杂质的离子注入工艺也存在很难控制的问题,很容易造成管子门限电压过大等不良结果。

本文引用地址:https://www.eepw.com.cn/article/104927.htm

其次,传统的SiGe PMOS硅应变技术也开始面临瓶颈,在32nm制程节点中,漏源两极中掺杂的锗元素含量已经占到了40%左右,很难再为沟道原子提供更高级别的应变.

其三,栅极氧化物的厚度方面也将出现发展瓶颈问题.IBM研发中心的高管Bruce Doris表示,栅极氧化物厚度减薄的速度已经跟不上栅极宽度缩小的步伐.

其它一些平面型晶体管所面临的问题也将越来越难解决.工作电压的不断升高,使芯片的功耗控制变得越来越困难;而且关键尺寸的缩小还会导致漏/源极电阻的不断增大.

那么业界有什么策略来应对这些挑战呢?

Intel的战略:22nm仍采用传统技术,15nm可能转向三门结构

据Intel表示,在下一代22nm制程产品中,他们仍将继续采用传统基于体硅的平面型晶体管结构(此前曾有传言称 Intel会在22nm制程中转向立体结构的三门晶体管技术),他们计划于2011年底正式推出22nm制程技术。而在今年的9月份,Intel已经展示过一款采用22nm制程技术制造的SRAM芯片,这种芯片的存储密度为364Mb,内含29亿个晶体管,并且采用了Intel第三代gate-last HKMG制程技术,门极绝缘层和金属栅极的主要部分在制造工序的最后几个工步制造成型,避开前面的高温退火工步(45/32nm中使用的前代技术则只有金属栅极才在最后几个工步制造成型)。

至于15nm制程节点,Bohr表示,Intel目前正在考虑在15nm制程节点上要采用哪些新的制程技术以满足要求,他认为:“全耗尽技术对降低芯片的功耗非常有效。”不过 Intel目前也在考虑除此之外的多种可行性方案,比如是转向三门晶体管技术(三门技术其实与IBM的双门finFET同属finFET型晶体管,但由于对手将其双门技术命名为finFET,因此Intel便根据自己的finFET技术特点将其命名为三门技术),或者是转向全耗尽+平面型晶体管技术等等。据Bohr表示,Intel会在六个月之内就15nm制程节点将采用哪一种新技术做出决定。

评论