超能课堂(278):Intel核显是怎样逐步进化成Xe的

每次看显卡市场占有率的图表,最大的那家不是NVIDIA也不是AMD,而是Intel,它占据了整个显卡市场的大半壁江山,原因当然是因为他们家的主流处理器基本上里面都会带一个核显,而他们家的处理器也占市场大头,占有率当然高。

其实早在1998年,Intel就进入了显卡市场,推出了Intel i740独立显卡,随后它被整合进了810/815芯片组,从此就诞生了Intel的集成显卡家族,在那个时代核显还是整合在北桥内的,直到2010年的Clarkdale处理器开始这个集显才进入CPU内部。现在最新的Xe架构核显已经是Intel的第12代显示架构。

曾几何时Intel的核显每年都会随酷睿系列处理器一同升级一次,直到第八代的Cannon Lake卡壳,让Gen 9.5核显伴随了我们很久,移动平台直到2019年推出的Ice Lake处理器才开始恢复核显的升级,桌面平台是到今年的Rocket Lake直接跳到最新的Xe架构。

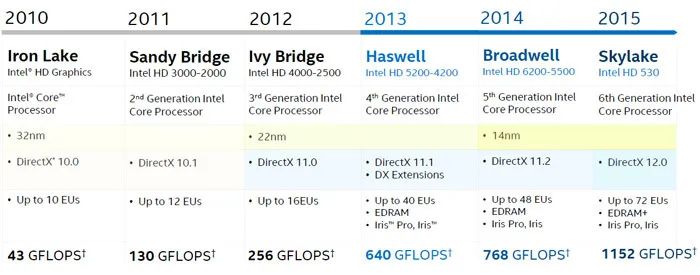

早期Intel核显的时间轴

不过呢,与CPU的性能方面被骂挤牙膏不同,核显的性能每代提升都挺大的,下面我们就来回顾一下Intel的核显进化历程。

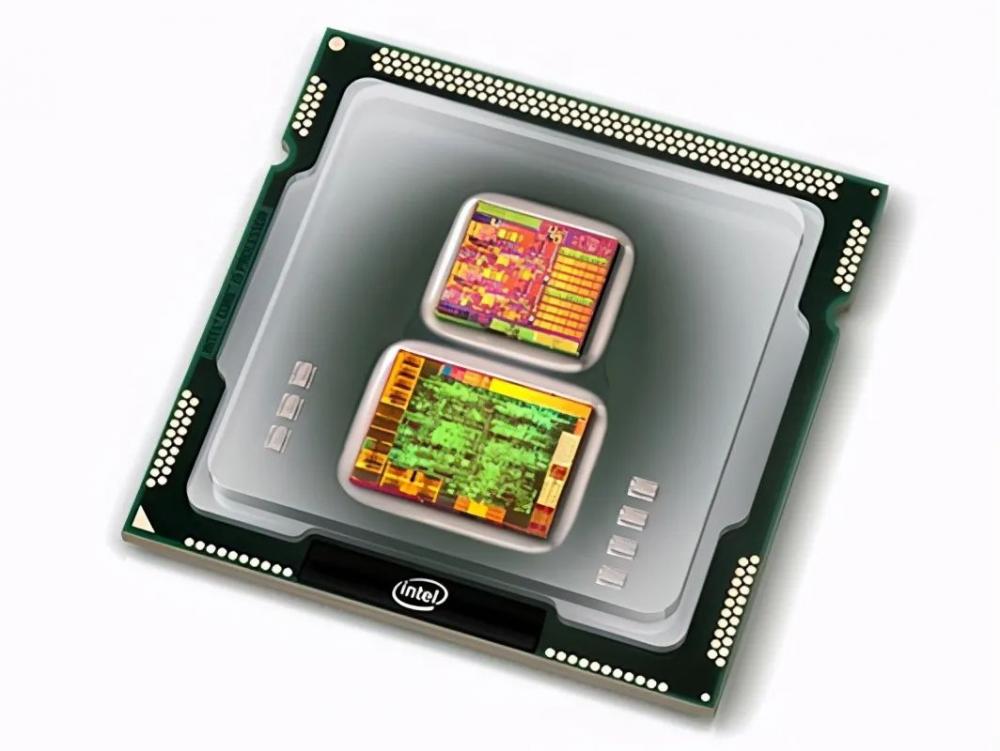

Gen5:Clarkdale

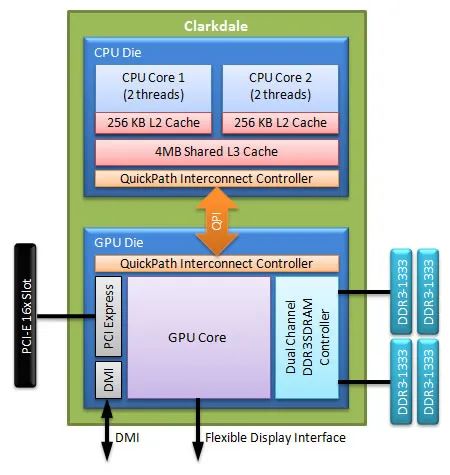

2010年推出的Clarkdale处理器确实首款整合GPU的CPU,这款处理器由32nm制程CPU Die和45nm的GPU Die共同封装在一块PCB上组成,两颗芯片使用QPI总线相连,其实当年看Clarkdale感觉是坑爹的Intel又在玩胶水,但现在看惯了AMD的Zen 2/3处理器之后再看它,感觉Intel当年的做法其实也没啥。

Clarkdale内核结构图,GPU Die上包含了PCI-E控制器和内存控制器,其实就是一个北桥芯片

Clarkdale系列处理器只有双核的型号,有Core i5-600和Core i3-500两个型号,在LGA 1156时代四核处理器是没有整合GPU的。

当时的Intel把Clarkdale上的GPU统称为“Intel HD Graphics”,这名字一直用到现在。而这个GPU其实就是G45上的X4500 HD的升级版,EU增加了两个达到了12个,核心频率最高可以到900MHz,支持Hierarchical Z(层次Z缓存算法)与Fast Z Clear(快速Z清除)技术,支持DX10、SM4.0,支持OpenGL 2.1,移动版处理器的GPU可以通过Turbo Boost动态调整频率,而桌面版不行。

Gen6:Sandy Bridge

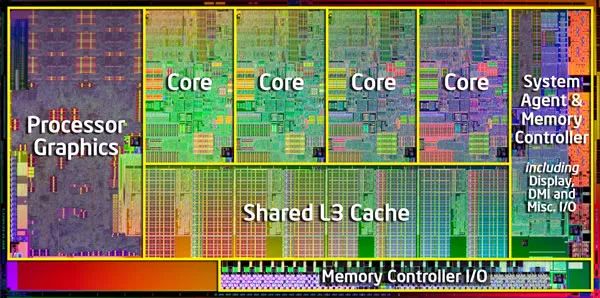

Sandy Bridge核心图

正在把CPU和GPU做到同一块芯片上的是在2011年上推出的Sandy Bridge架构处理器,CPU、GPU、内存控制器、PCI-E控制器全部整合到一个核心里面,它的最大改进在于三级缓存改用了环形总线设计,并且其核心、GFX以及显示/媒体控制器可共享L3高速缓存。

Sandy Bridge的GPU主要包含了指令流处理器、媒体处理器、多格式媒体****、执行单元、统一执行单元阵列、媒体取样器、纹理采样器以及指令缓冲等等,架构与上一代相比有了较大修改。

Sandy Bridge按照型号划分了标准版以及“K”系倍频解锁版本,标准版本GFX命名为HD Graphics 2000,而唯独K系列所拥有的GFX为等级更高的HD Graphics 3000,两者的区别是前者拥有6个EU,而后者则达到了12个,全面支持Turbo Boost动态调整频率,最高频率可达1350MHz,支持DX10.1、SM4.1,支持OpenGL 3.0,性能上HD Graphics 3000比上一代有了翻倍的增长。

此外这一代核显还增加了Quick Sync转码加速技术,利用内置的编码器可以支持MPEG2、VC1和H.264视频各种的硬件编码,Sandy Bridge所整合的图形核心已实现了视频解码和编码两部分的硬件加速功能,可为用户在视频转码时节省更多的时间。

Gen7:Ivy Bridge

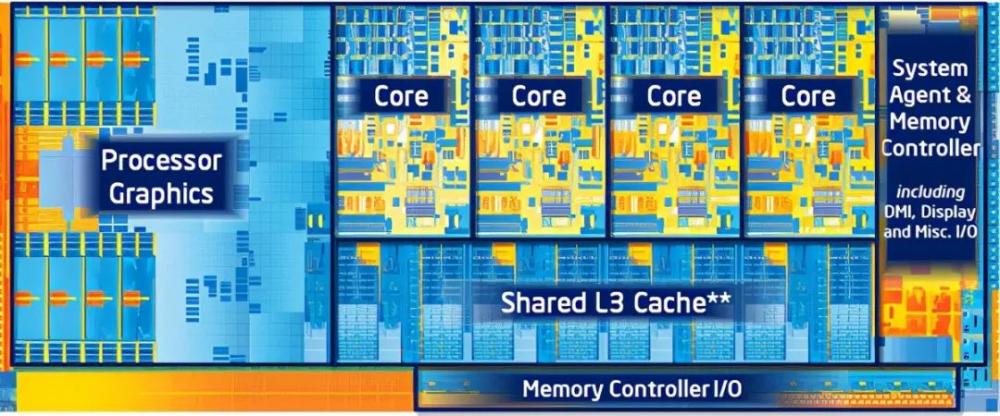

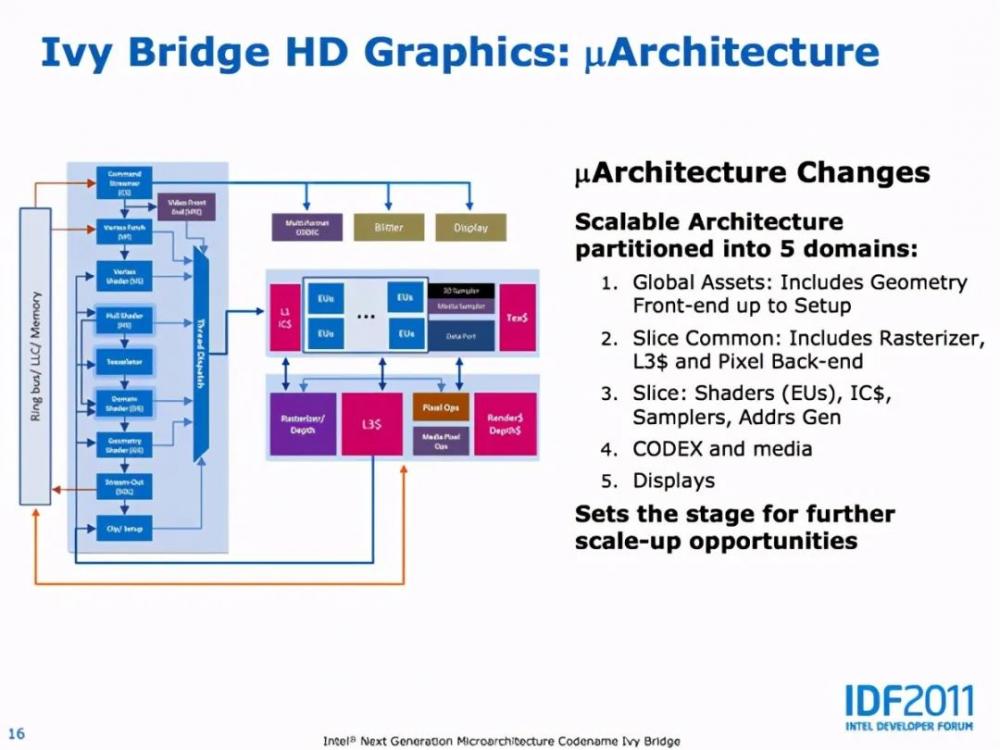

Ivy Bridge架构图

在Ivy Bridge上Intel针对核显的改进还是两个方向,首先是进一步提高GPU的性能,并且让其支持DX11,第二点则是继续提高核显的功能,多屏输出、高分辨率支持等。

Ivy Bridge的GPU增强了几何前端、光栅化、像素后端处理、采样器、寻址单元的并行运算能力,每周期可以执行2个MAC操作,GPU可以直接读取L3缓存中的数据,图形单元新增两个可编程操作以及一个固定功能单元以支持曲面细分计算,并在解码与显示功能上做了升级。

同样的核显也分为两种,分别是有16个EU单元的HD 4000和6个EU单元的的HD 2500,“K”系列处理器用的是HD 4000而其他处理器用的是HD 2500,最高频率与SNB时代一样是1350MHz,支持DX11、SM5.0,支持OpenGL 3.2,性能上HD 4000比上一代的HD 3000提升是67%。

Ivy Bridge支持Quick Sync 2.0编码加速技术,与第一代相比,2.0版不仅速度更快,而且画质也会更高。视频输出方面也从原来的双屏上升到三屏输出,最大分辨率从原来的2560*1600上升到4k*4k级别。

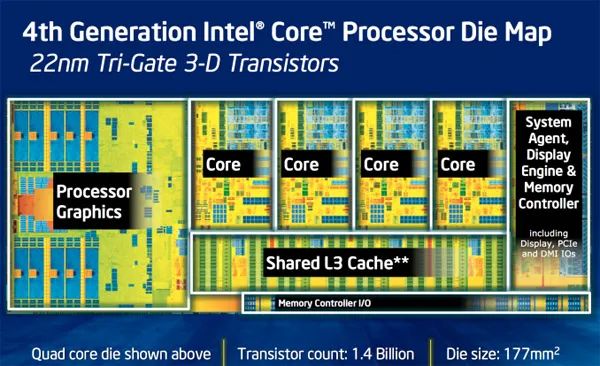

Gen7.5:Haswell

Haswell架构图

Haswell采用的是Gen7.5核显,这一代开始Intel的核显开始了模块化、可扩展的设计,Haswell的显示核心采用两级EU团簇结构设计,上级的叫Slice,下级的叫Subslice,每个Subslice拥有10个EU,2组Subslice单元组成了1组Slice单元,这一代在GT1和GT2两个级别之上又诞生了GT3核心,从此Intel就走上了暴力堆砌核显规格的道路。

Haswell的GT1、GT2、GT3核显分别拥有10个、20个和40个EU单元,此外还有一个带嵌入式eDRAM的GT3e,核显集成了128MB eDRAM,位宽512bit,带宽可达64GB/s,这个嵌入式eDRAM是作为L4缓存存在的,可以同时提升CPU和GPU性能。

Intel的核显一直以来都用HD Graphics来命名,不过与NVIDIA的GeForce还有AMD的Radeon相比这个名字还是不够霸气,因此从Haswell处理器的核芯显卡开始,英特尔将引入新的名字“Iris”和“Iris Pro”,中文名为“锐炬”和“锐炬Pro”,分别对应GT3以及GT3e核显,具体型号则是Iris Graphics 5100和Iris Pro Graphics 5200。

这一代的桌面版酷睿处理器基本上都是使用GT2核显,型号是HD Graphics 4600/4400,后者只用在Core i3-41xx系列处理器上,只有16个EU,对非K系列处理器来核显性能是较上一代有大幅提升的,而真正需要高性能核显的也是Core i3那种级别的,高端处理器基本都是配个独显。

奔腾和赛扬处理器配的是GT1核显,而这一代最强的GT3e核显只出现在两款桌面级处理器上,就是Core i7-4770R和Core i5-4670R,然而这两个都不零售,是针对OEM市场的产品。

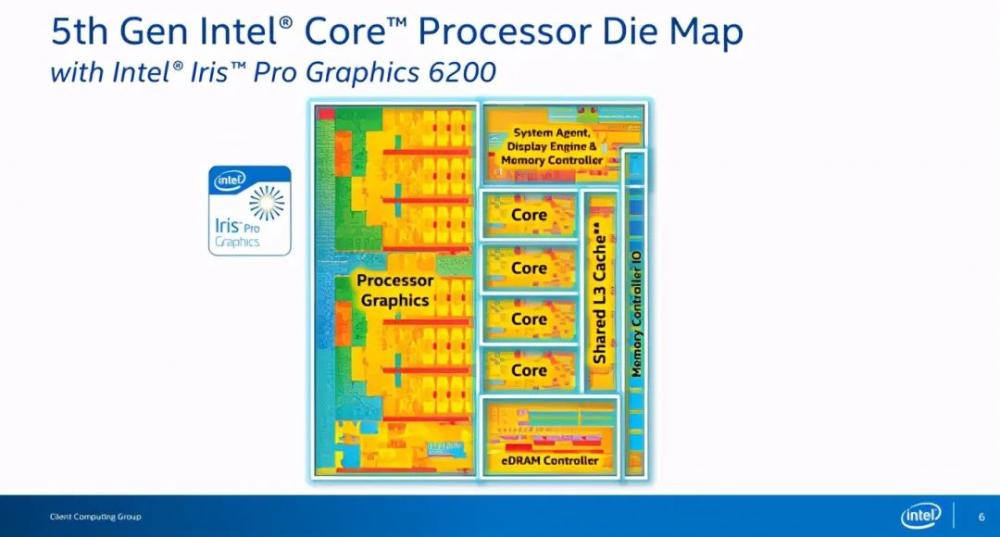

Gen8:Broadwell

Broadwell-H内部结构

Broadwell主要都是面向移动市场,在桌面零售市场上其实就只有两个CPU,Core i7-5775C和Core i5-5675C,配备Intel目前最强的Iris Pro 6200核显,拥有128MB的eDRAM缓存,另外倍频无锁,可进行超频。

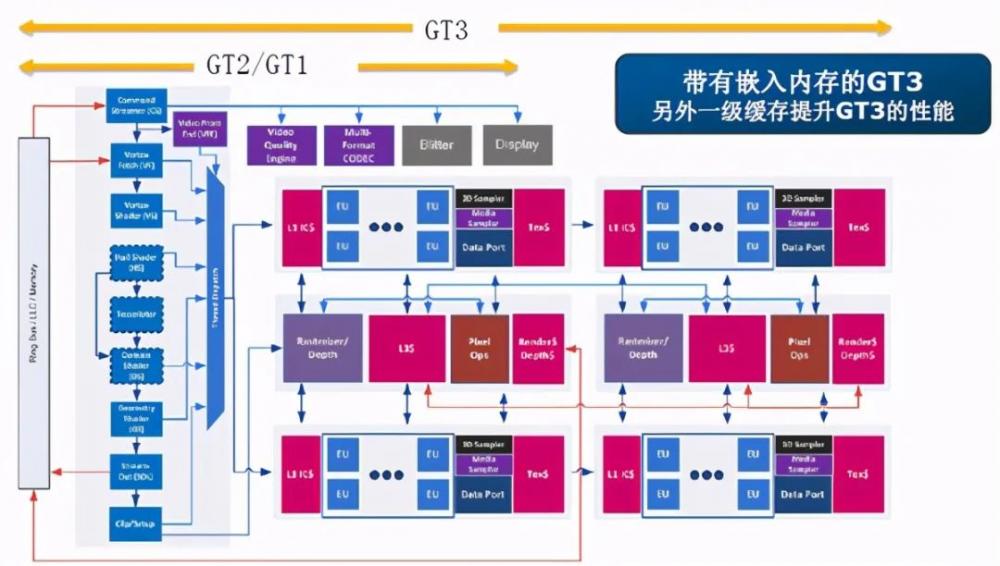

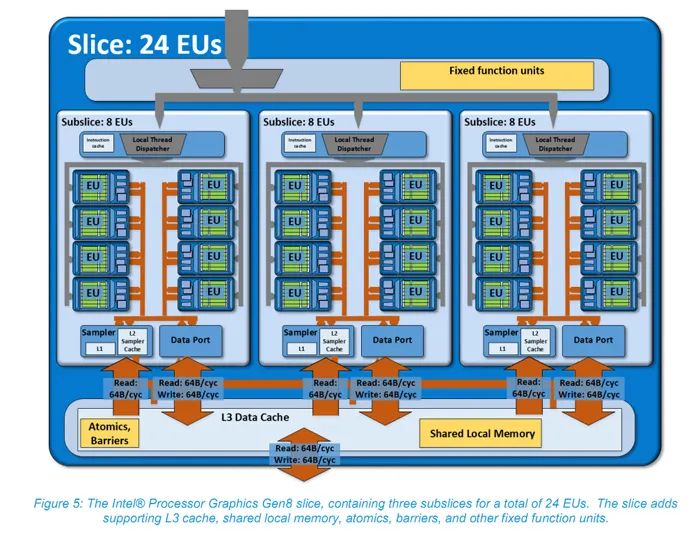

Broadwell上的Gen8 GPU架构示意图

Broadwell上使用的是Gen8图形核心,Intel重新设计了Subslice单元,每组的EU单元从之前的10个下降到了8个,在同样的采样器及调度器下这意味着每个EU单元的效率提升了,而弥补EU数量可以通过提升Subslice单元 总数来完成,所以Broadwell的1组Slice单元有3组Subslice单元,EU单元总数是24个,Broadwell的GT1、GT2、GT3核显分别拥有12个、24个和48个EU单元。

桌面零售版那两个配备的Iris Pro 6200属于带eDRAM的GT3e核心,得益于核心规模的大幅提升,Core i7-5775C的核显性能较上一代Core i7-4790K提升了将近80%,性能甚至吊打之后桌面的各种Skylake衍生物,不知道它和Rocket Lake的Xe核显比起来有多大差距。

Gen9:Skylake

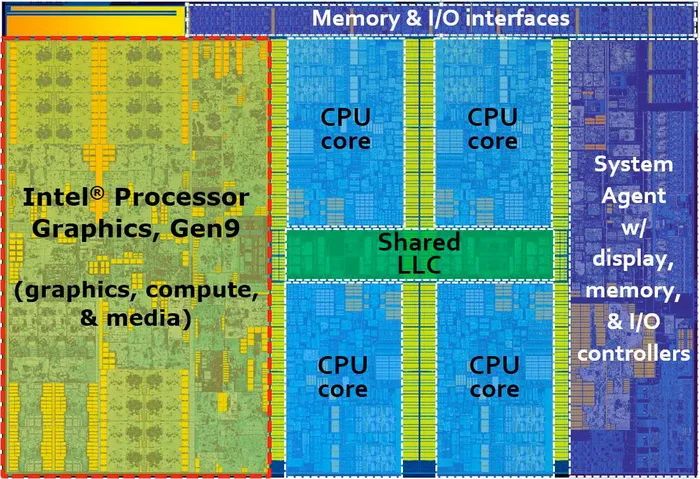

Skylake处理器核心

Skylake使用的Gen9代GPU其实与Gen8有很多地方都是相似的,每组Subslice单元依旧是24个EU,但是最多可以扩展到3组Slice单元,也就是说最多会配备72个EU单元,因此Skylake也多出GT4这个级别的核显。

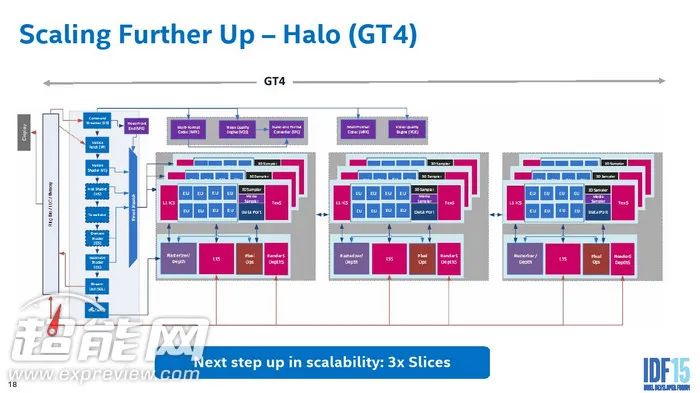

GT4核显可以支持3组Slice单元,72个EU单元

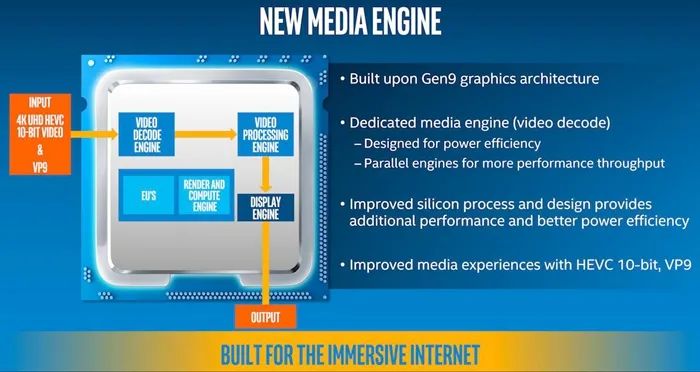

Skylake的Gen9架构支持DX12、OpenCL 2.x、OpenGL 5.x、Vulkan等图形规范,支持新的编译器堆栈,功耗范围从4W-65W+不等。此外,Gen9还支持HEVC/H.265、AVC、SVC、VP8、MJPG硬件加速,支持摄像头RAW架构。

多媒体方面,Gen9架构支持单一固定功能单元以降低功耗,Quick Sync转码单元也设计了固定功能的编码器以降低功耗、延迟。此外,Gen9的视频解码、转码加速还支持了HEVC(H.265)、VP8、MJPEG等标准。

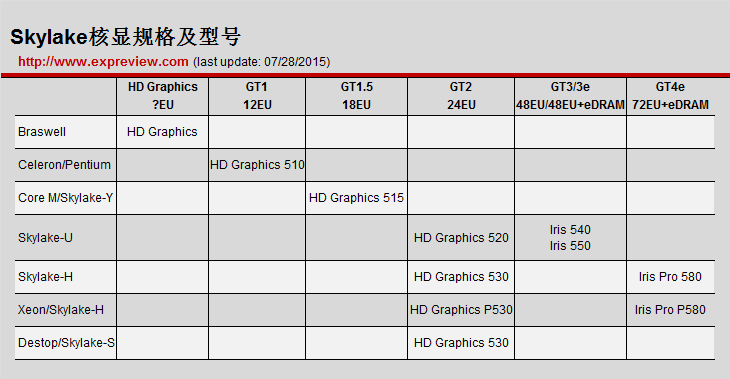

Skylake处理器上启用全新的核显命名

然而GT3/GT3e/GT4e这样的高性能核显只使用在移动版处理器上,桌面版的Skylake处理器基本上都是使用只有24EU的GT2,虽然较桌面版Haswell来说性能还是有所提升,但是幅度只有20%。另外还有两个“P”后续的处理器用的是GT1核显。

Gen9.5:Kaby Lake/Coffee Lake/Comet Lake

提到Gen9.5核显就不得不说陪伴大家多年的HD/UHD Graphics 630了,它用了Kaby Lake、Coffee Lake、Comet Lake三代架构,从桌面的第7代酷睿一直用到第10代酷睿,至今依然是Intel的现役产品。

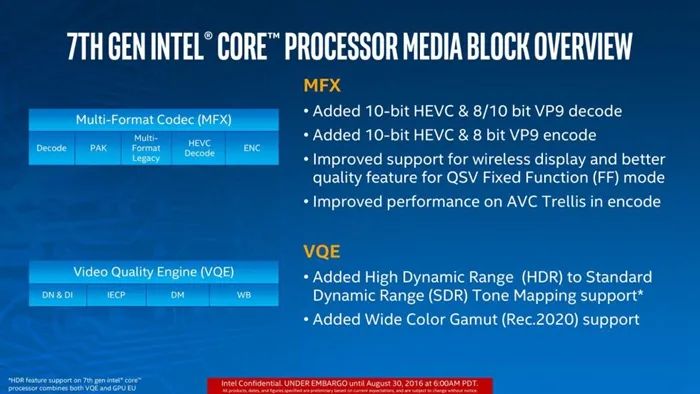

Gen9.5增强了视频硬解码能力,使用了更强大的MFX多格式媒体编****硬件模块,支持10bit HEVC、8/10bit VP9视频格式的硬件解码,10bit HEVC、8bit VP9视频格式的硬件编码;增加了Intel无线高清显示技术支持,提高了AVC编码效率。

对VQE视频质量引擎增加支持HDR和SDR,支持Rec.2020更宽广的色域,使得输出视频画面色彩具可塑性。从第八代酷睿处理器开始核显名字从HD Graphics变成UHD Graphics,其实就是视频输出接口增加支持HDMI 2.0/HDCP 2.2标准,并没有什么大变化。

而在Gen9.5核显之后,因为Intel自己的10nm工艺难产,导致Gen10核显伴随Cannon Lake处理器一同胎死腹中,使得Gen9.5核显从2017年开始一直服役至今。

Gen11:Ice Lake

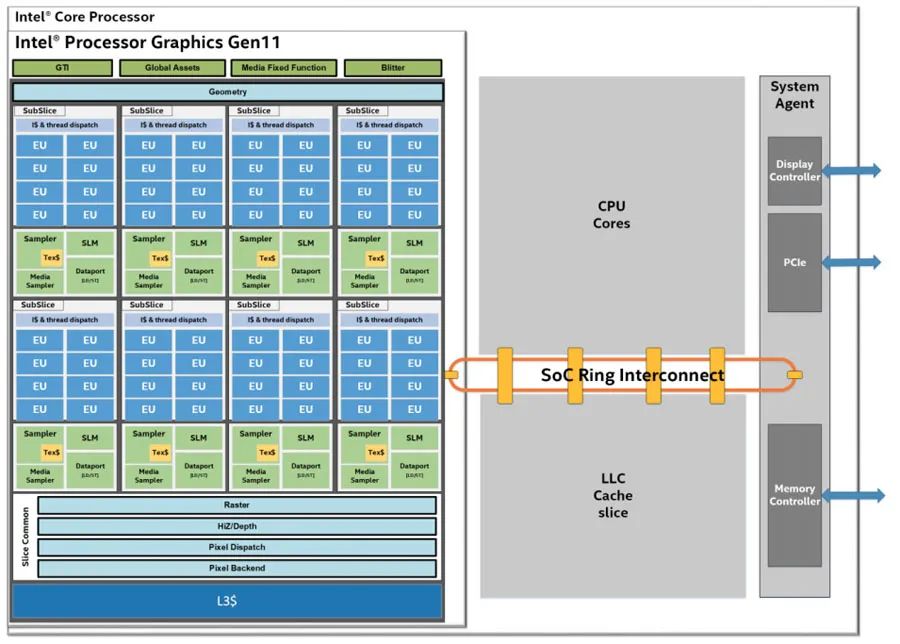

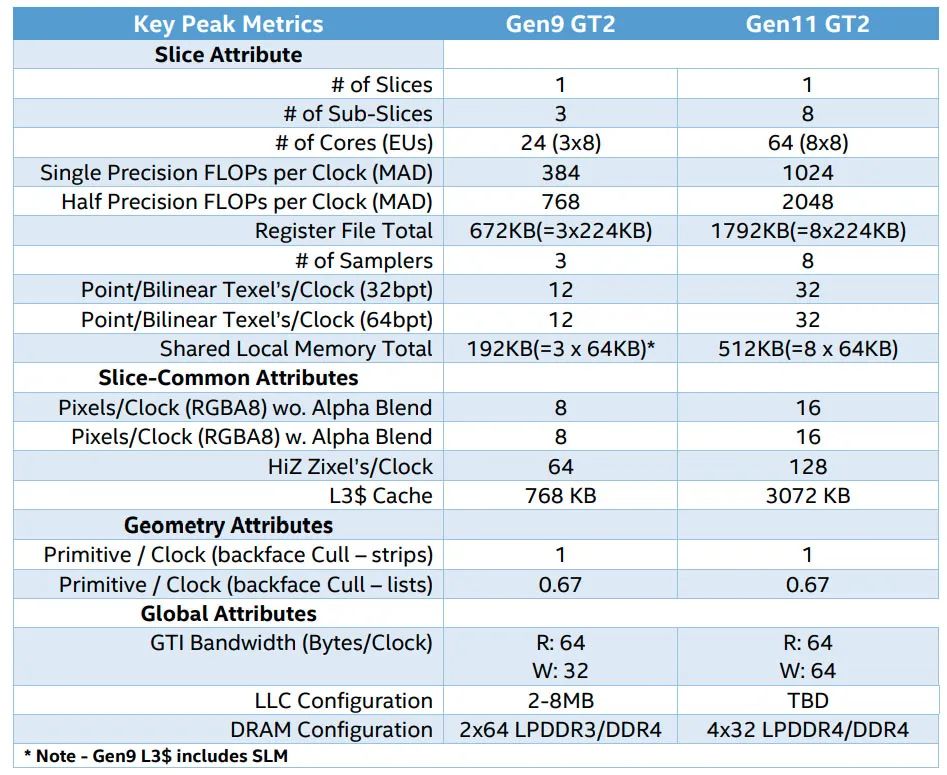

沉寂多年那之后 Intel的10nm工艺终于熟了,Ice Lake架构携同Gen11核显一同出现,得益于10nm工艺的高晶体管密度,Gen11的EU数量大幅提升,最大可以达到64组EU, 核显首次达到了1TFlops的计算性能。

不过Ice Lake处理器只有用在第10代酷睿低功耗处理器上,桌面与移动标压处理器都是Comet Lake,所以用Gen11核显的处理器并不多,Intel一共提供了G1、G4和G7三种配置的核显,分别有32/48/64组EU,低端的G1命名仍为“UHD”,而G4和G7都以“锐炬Plus”的品牌出现。

在架构上,Gen11核显通过增加单个Slice中含有的子Slice来扩大规模,使得每周期的计算次数增加。其次是在缓存系统上做文章,扩大了三级缓存的容量,Intel方面公布的是EU的三级缓存有3MB,并且还有0.5MB的本地共享内存。另外还有通过处理器的内存控制器升级,能够用上更高的内存带宽。

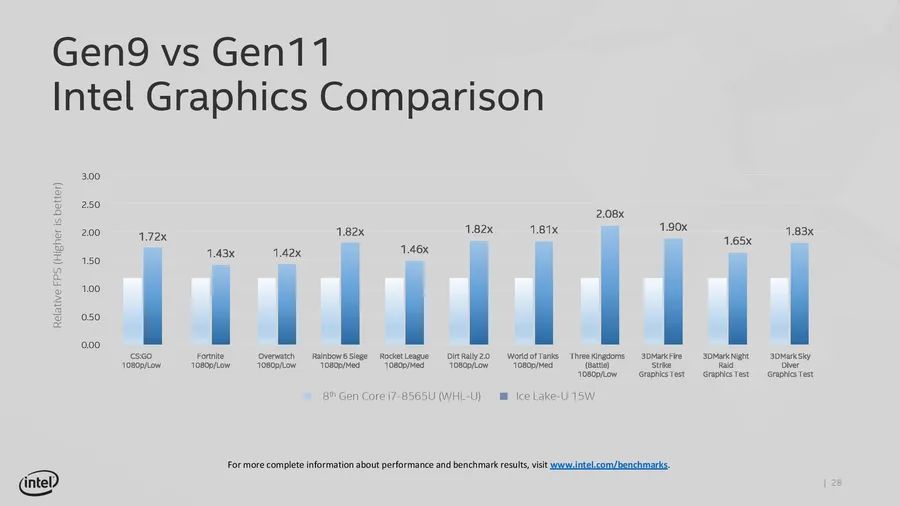

相比8代酷睿处理器上搭载的Gen9核显,官方宣称可以提供平均约1.8倍的帧率。

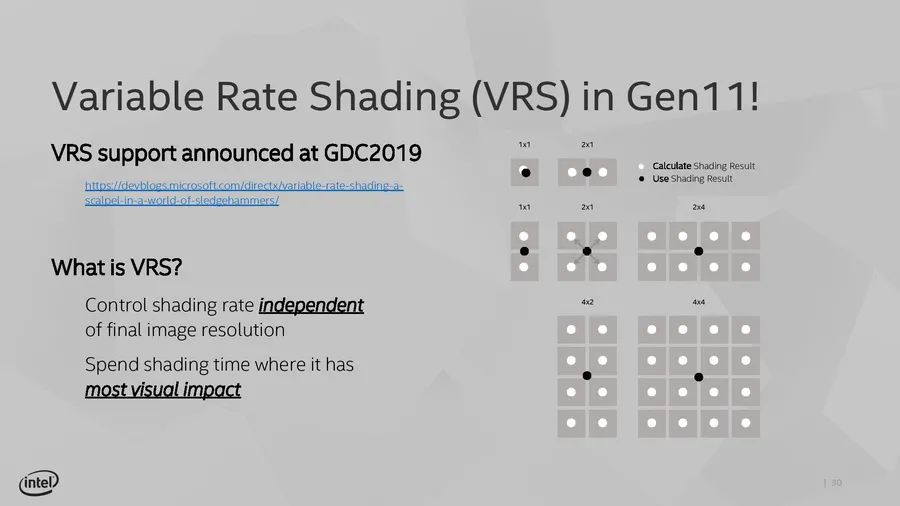

此外Gen11核显支持VRS可变速率着色,它可以在不重要的画面上面节约一定的GPU资源,使这部分GPU资源参与更加重要的部分画面的渲染中,从而提高了整体的帧数,并且根据Intel的数据, 在支持VRS的游戏中可以让帧数最大提高了30%。

在视频接口方面,Gen11核显新增支持HDMI 2.0b和DisplayPort 1.4 HBR3,输出的最高分辨率和帧数有所提升,并且支持HDR。

在视频硬件编码部分,也就是Intel QuickSync特性使用的独立硬件电路上,Gen11核显也有比较大的改进,现在支持两条HEVC 10-bit同时进行编码,在YUV444的情况下最高支持两条4K60帧视频流,或者一条YUV422的8K30帧视频流。

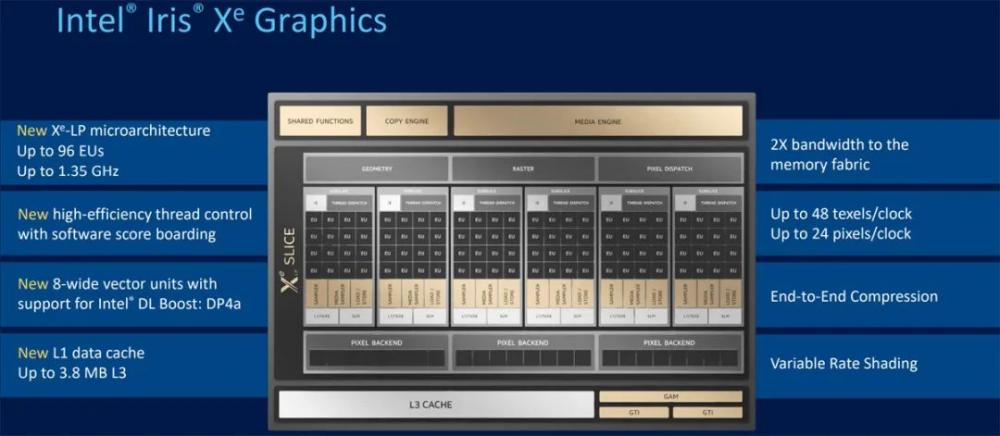

Gen12:Xe

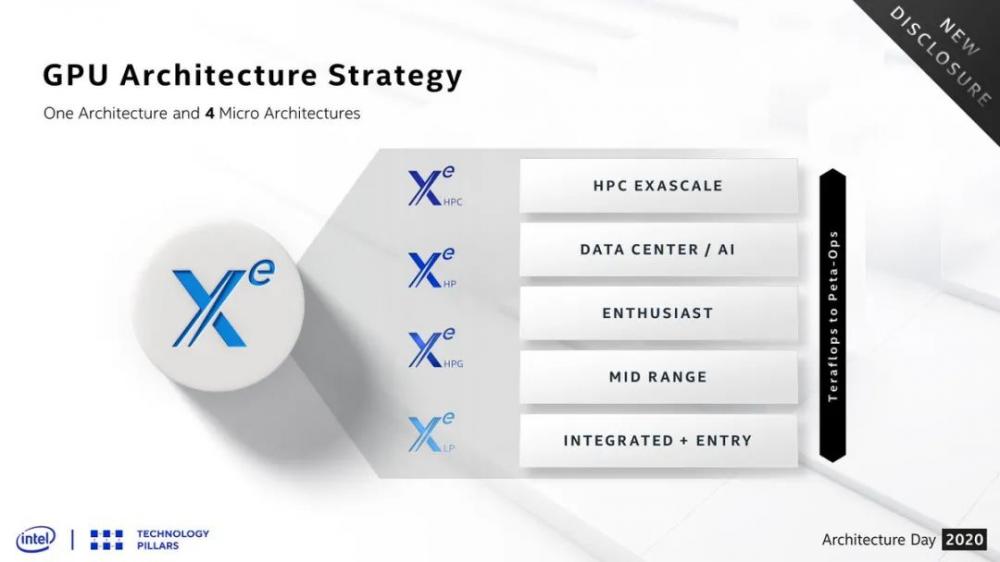

Intel的第12代显示架构名为Xe,它可以说是Intel这些年来最有野心的产品,Intel将Xe GPU的架构描述为可扩展的向量-矩阵架构,它的高度可扩展性让它能够针对不同市场推出不同分支的架构和产品,从面向高性能计算市场Xe-HPC,面向数据中心、AI计算的Xe-HP,再到面向游戏玩家的Xe-HPG和面向移动端的Xe-LP,多种多样。

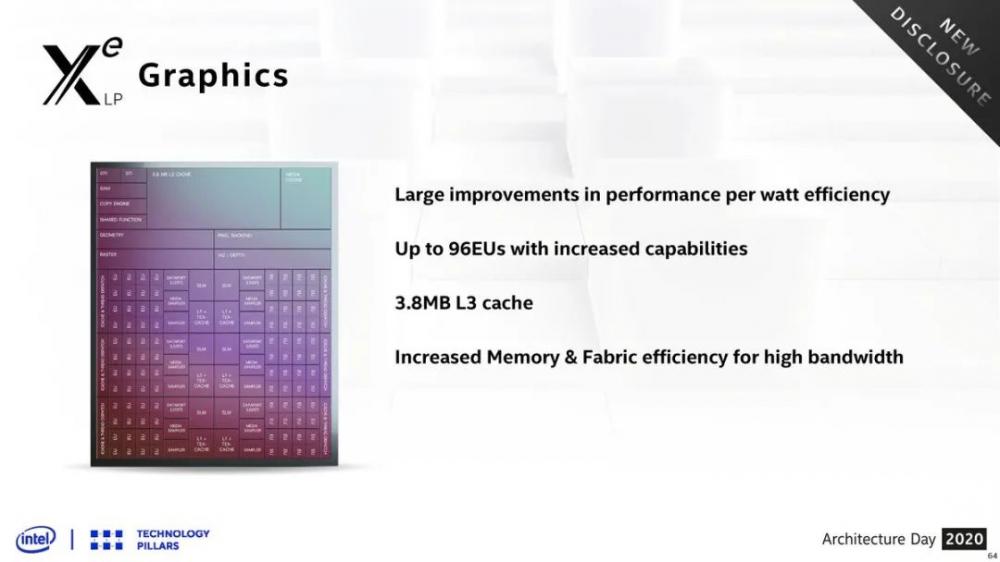

Tiger Lake与Rocket Lake处理器上所用的Xe-LP架构是Xe架构中面向于 低功耗产品的变种,架构的主要关注点是能效比,也就是要在尽量低的能耗下提供尽量强的性能。

Tiger Lake-U集成的Xe-LP GPU拥有6组Slice共96组EU,在规模方面较Gen11核显大了50%。而Tiger Lake-H与Rocket Lake上的核显则只有2组Slice共32组EU,但与Comet Lake处理器相比图形性能依然提升了50%。

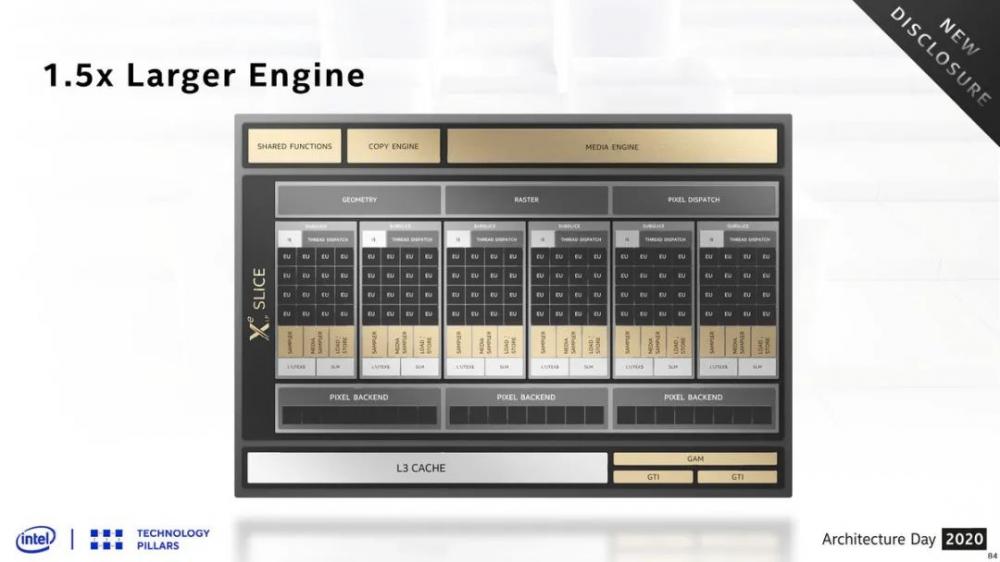

在Xe-LP上,Intel大刀阔斧的对EU内部进行了调整,首先Gen 11的一对一的线程控制单元现在变成一对二了,也就是一个线程控制单元实际要负责两个EU的任务。再往下,到具体的ALU上面,现在每个EU中含有8个用于处理浮点或整数指令的ALU,另外还有两个只针对扩展数学指令的ALU,从原本的4+4结构变成了8+2,而且两种类型的指令可以并行处理了。

在Xe-LP上,Intel大刀阔斧的对EU内部进行了调整,首先Gen 11的一对一的线程控制单元现在变成一对二了,也就是一个线程控制单元实际要负责两个EU的任务。再往下,到具体的ALU上面,现在每个EU中含有8个用于处理浮点或整数指令的ALU,另外还有两个只针对扩展数学指令的ALU,从原本的4+4结构变成了8+2,而且两种类型的指令可以并行处理了。

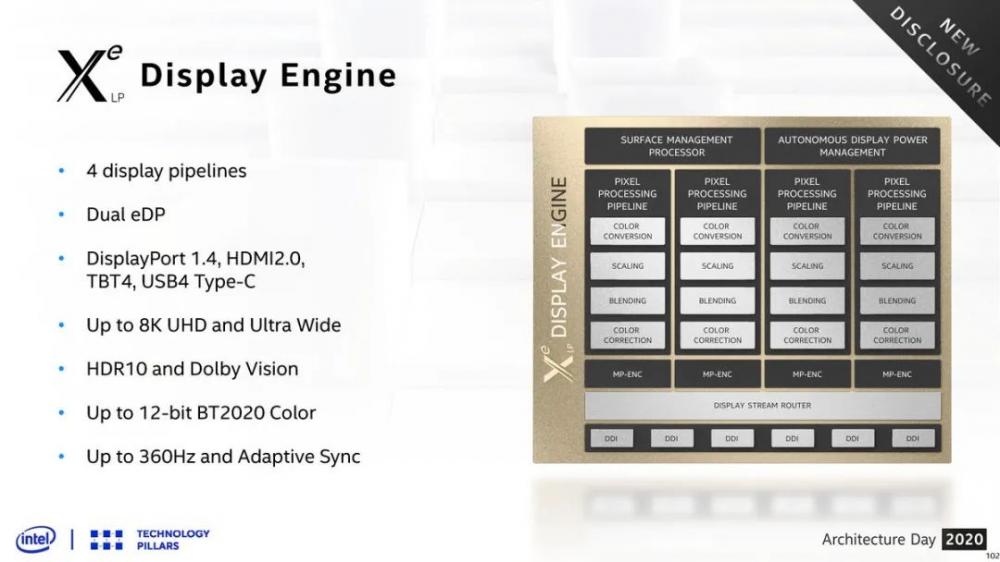

显示引擎方面,有四条4K分辨率级别的处理管线,支持两条eDP,外部输出接口则是支持DisplayPort 1.4和HDMI 2.0,当然,具体的输出接口可以是DP和HDMI,也可以是USB-C。其他像是8K输出、HDR10、Dolby Vision、12-bit BT2020色域和自适应同步都有支持,对显示器的刷新率,最高可以支持到360Hz。这里很可惜的是,我们没能见到原生的HDMI 2.1支持,厂商可能会通过转接芯片去做支持。

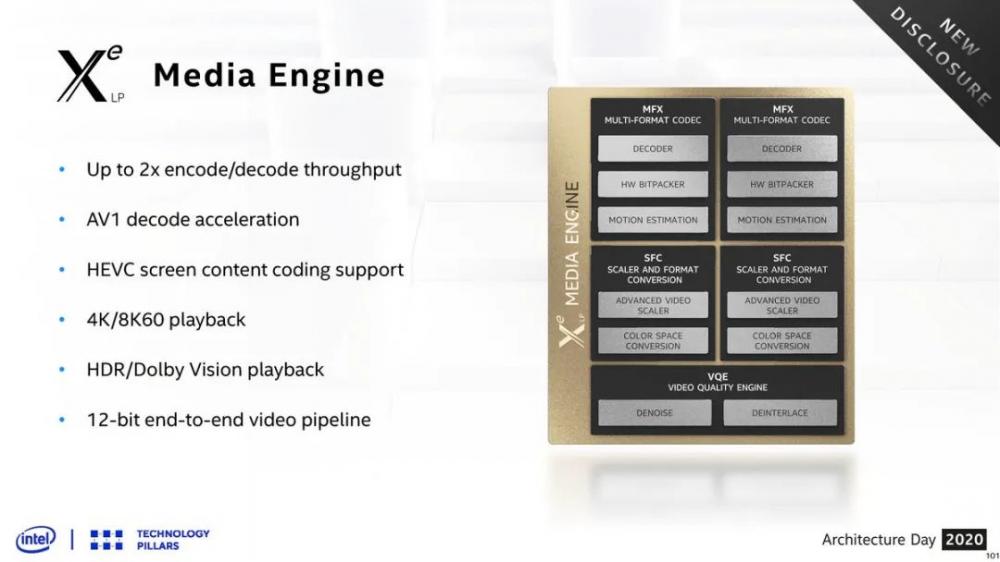

媒体引擎方面,整个处理管线的编解码性能提升了一倍,色深的支持升级到了12-bit,并且能够支持HDR/Dolby Vision的回放。这里还有一个亮点是对AV1做了硬件解码支持,这是一个面向于未来的特性。

目前大家见到的Xe核显以及那个DG1独显只是Intel的Xe计划的第一部,如无意外的话今明两年内我们会见到面向游戏玩家的Xe-HPG进入市场,届时我们将会在独显市场见到三足鼎立的情景。

其实Intel在早期CPU与核显的搭配是有些问题的,越强的CPU配越强的核显,但实际需求明显是反过来的,还好这个问题早就改过来了,现在的11代酷睿处理器就很明显,只有四核的Tiger Lake-U配的是拥有96组EU的GT2核显,而Rocket Lake-S与Tiger Lake-H这些八核处理器则只配32组EU的GT1核显,因为Tiger Lake-U是用在轻薄本的,多数没有独显,得靠自己的核显,而Rocket Lake-S与Tiger Lake-H则多数会配独显,核显的性能就显得不那么重要了,稍微精简一点也没所谓。

下一代的Alder Lake会继续使用Xe架构,同样的核心数量更少的Alder Lake-P会配更强劲的GT2级别核显,核心数量更多的Alder Lake-S则配GT1级别核显,再下一代的Raptor Lake估计会用改良的版本。至于Xe架构以后会如何进化,由于Intel从AMD的图形部门挖了不少人,所以大家其实可以参考AMD的GCN,预计会一步步慢慢优化挖掘Xe架构的潜能,当然以Intel的家底,一边优化Xe的同时并行开发另一种架构的GPU不是不可能的。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。