条条道路通节能 节能的挑战与机遇在何处

摩尔定律表明,每24个月(后来业界修正为18个月)IC上可容纳的晶体管数量增加一倍,性能也将提升一倍。2000年底网络泡沫破灭后,人们最为关心成本,其次是功耗和性能。这两年,随着便携式产品的异军突起和全世界节能环保的要求,降低功耗成为了业界普遍关注的大事。

近日,笔者采访了众多公司,看到他们非常重视节能和环保。西谚说“条条大道通罗马”,由此引申到节能环保,我们可以通过很多方法来实现节能。

众多公司在Electronic Summit2008电源讨论会上发言

(自左至右的代表来自:安森美、Intersil、Mentor、Qimonda、NS和Cadence)

节能的设计方法学

National Semiconductor公司(以下简称NS)全球伙伴关系市场行销经理Rick Zarr从多个角度谈了看法。

●我们有时从系统架构层面来实现节能。一个实例是半导体的性能、温度和电源电压的关系。我们的设计出发点是有效工作状态。半导体产品的性能各不相同,其中大部分是CMOS电路,其性能往往要高于你的设计目标。如果你能够适应各种产品的性能特性,就能实现产品的整体性能优化。

●在芯片层面上,也可以采用新的设计哲学。当前设计方面的一个挑战是,如何突破许多工程师在思路上的线性化框架。工程师们必须把思路延伸到机箱之外。NS现在具有可以在芯片级完成这一工作的产品,即电源电压可自适应缩放的产品。但我们还需要在更高层次上的产品,此时软件就将发挥作用。

●散热问题,这与电源转换效率有关。当接近理论极限时,设计的回报就很低。由于能量的转换必然伴随着发热,架构设计师和工程师研究我们消耗了多少能量,但是那部分能量又该如何去除?如果你的应用空间固定,而冷却的能力有限,即解决问题的方法受到了约束,因此,这是一个很大的挑战,对于那些要设法利用现有基础设施的人们来说尤为如此。

●微量节能。实际上,微量节能也能带来巨大的影响,因为其数量会随着用户数量增加而成倍增长。如果你能在保证性能的情况下挤出一点功耗来,无数的功耗累积起来效果巨大。据美国能源部的一个统计表明,如果美国的每一户家庭把一只灯泡用CFL(节能荧光灯)—其效率是白炽灯的两倍—来取代的话,节约下来的能量将足以供300万户家庭使用。这个例子说明,设计工程师们面临的挑战,不仅是那些巨大的挑战—如何用更低的功耗获得更高的性能,也包括如何实现环保等。

便携式电源转换拓扑结构经验

Intersil公司负责便携式业务的高级产品市场行销经理Andrew Baker说该公司把降低电源划分成为两个部分:

●系统级及软件性的功耗管理;

●硬件的功耗管理。

设计者需要把这两部分有机地组合起来,以实现优化的功耗特性。

从系统设计的角度来看,架构及其划分很重要,设计人员需要确定哪些功能是必需的。例如,手机在大部分时间里是处于待机状态的,因此可以把大部分与RF部分无关的电路关闭。你可以在架构上考虑电能是如何从电池转换为电路电源的,线性的还是开关式的,软件必须管理好这些。软件是确保何时应该按照何种模式工作的关键,有的软件工程师认为它就是宇宙的中心,在大多数情况下的确是这样。软件需要针对实时管理操作进行优化,考虑到全功耗、低功耗、休眠、深度休眠,这些就是人们目前所能想到的处理功耗问题的系统解决方案。我们还应把系统划分为多个微处理器,它们甚至可以在同一片芯片上,让他们能以不同的时钟速度工作。这也是一种优化系统性能的方法。

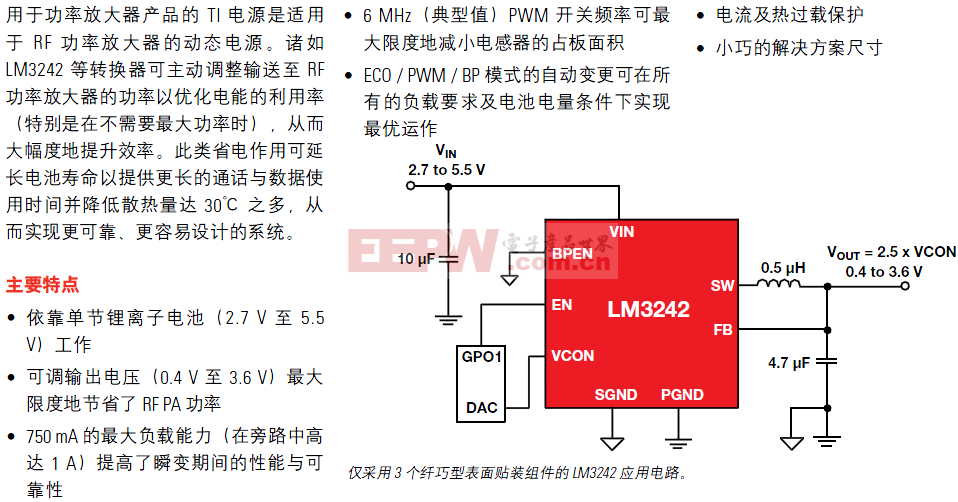

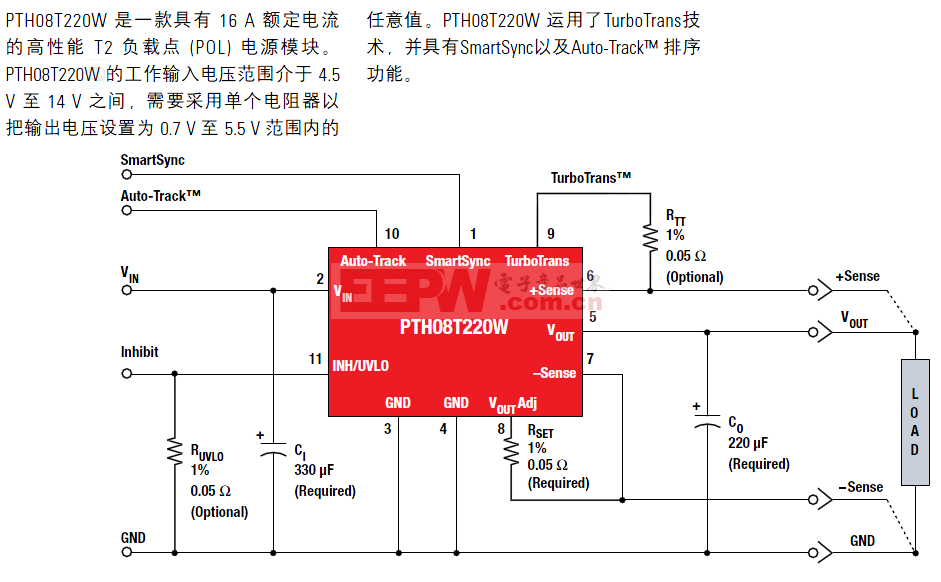

在硬件方面,你可以有多种选择。市场上有多家厂商、多种架构的解决方案。例如,开关式稳压器是手持式装置中常见的一种用于提高效率的手段,但市场上也存在一些线性的、成本更低的解决方案,有时它们更优化。因此架构的选择对于效率极为关键。电源管理方面,你可以采用多种模式。开关稳压器有两种模式:PWM(脉宽调制)和PFM (功率因子模块),PWM将为满负载条件服务,而PFM将用于轻负载条件。甚至还可以有第三种模式,如LDO(低压降)。事实上低压降的电源效率极高,可避免开关稳压器在开关中消耗的能量。例如,如果你的系统中已经有DC-DC变换器了,你还可以LDO作为第二级。例如,你可能希望系统的内存以1.8V工作,你现在已经有了1.8V的电压轨,而现在又需要为低压的内核供电,于是就可以用一个LDO 来为其提供一个1.2V的电压。这就是一个将两种拓扑结构组合起来,以达到优化的例子。

模拟IC

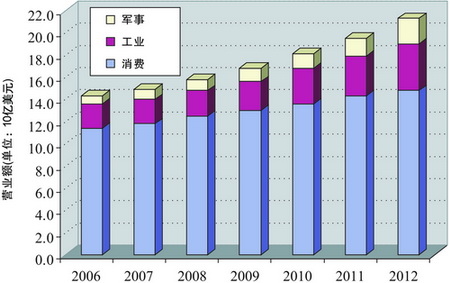

图1 世界电源市场

FPGA

一整套方案实现节能

Actel公司的总裁兼CEO John East认为,节电是件很复杂的事,需要从上百个角度去考虑解决问题,例如噪声、散热、工艺、材料、封装等问题。

Actel CEO John East:节能可从上百个角度考虑

Actel公司作为FPGA芯片解决方案厂商,认为低功耗往往不仅是一个芯片低功耗,更涉及到一整套的解决方案。以Actel为例,采用的技术是Flash FPGA,产品有两类:IGLOO是FPGA家族中超低的功耗产品,静态功耗达到0.05mW/百万门;加入了智能系统和功率管理的Fusion可编程系统芯片是第二个产品线;除此之外,还有功率优化的设计工具Libero IDE、低功耗的ARM Cortex-M1核,智能功率IP,以及号称业界最小的FPGA封装。

制程提到40nm

Altera发布业界首款40nm FPGA和HardCopy ASIC,命名为Stratix IV FPGA和HardCopy IV ASIC都提供收发器,在密度、性能和低功耗上遥遥领先。尽管40nm时漏电流是个挑战,但是由于采用了应变硅技术,使功耗大大降低,Stratix IV预计比上一代产品功耗降低了1/2。“原来我们计划08年推出45nm制程”,Altera资深市场副总裁Jordan S. Plofsky说,“由于代工厂TSMC的工艺进步,今年初TSMC已把工艺提高到40nm”。与此同时,Altera还发布了Quartus II软件8.0,支持其40nm FPGA/结构化ASIC,延续了该公司在设计软件性能和效能上的领先优势。

Altera 资深市场副总裁Jordan S. Plofsky

不过,等待新产品需要一些耐心。Altera计划于2008年第4季度提供Stratix IV器件系列第一个型号的工程样片,HardCopy IV ASIC将于2009年第三季度开始接受客户投片。

加入IP核

Xilinx公司CEO Wim Roelandts说,Xilinx一直在把越来越多的硬核和软核加入FPGA之中,包括第三方的IP核。因为IP核改进性能、提高速度且降低功耗。软IP和硬IP是相辅相成的,当软件的效率没有足够高,用硬件实现;硬件效率虽高,但成本高一些。因此选择硬核还是软核需要综合考虑成本、效率等问题。

Xilinx CEO Wim Roelandts

例如,08年3月底Xilinx推出了Virtex-5的第四个平台—FXT家族,是基于PowerPC440处理器模块、高速RocketIO GTX收发器和专用XtremeDSP处理能力。尽管Xilinx也有MicroBlaze软IP核,但是其产品的有力补充。

存储器

DRAM节能与可扩展性

“人们可能会觉得存储器与功耗方面的挑战并无多大关系”,Qimonda(奇梦达)公司的高级市场行销总监Tom Till认为,“但存储器与功能间的关联性取决于所用的平台。现在IT业大量采用了服务器。有文献表明,DRAM的功耗在服务器群(farm)的功耗中的比重为10%~40%,这里可用一个平均值25%来表达。关于数据中心的运行成本,2005年有一个数据,全球的服务器群在电能方面的支出达到了72亿美元,而其中DRAM所占的25%的功耗,就足以证明其与这个行业的关联性。设计者首先考虑的问题是如何安排DRAM在服务器中所占的空间面积,但如果他能设法利用可以轻松获得的技术—这实际上是个设计中的选择问题—将功耗降低20%,就可以节省约3.5亿美元的成本。考虑到IT市场的繁荣景象,就不难想象电力方面的成本支出在过去3年中出现了多大幅度的增长。

从DRAM的角度来看,目标就是设法设计出标准的低功耗DRAM,并在其中集成部分自刷新等功能。这种核心技术和集成的功能集将让DRAM从以待机模式为中心的设计转移到以有效工作模式为中心的设计文化上来。这再次说明,这既不是技术,也不是设计,而是设计中的取向问题。

存储器的可扩展性也是非常重要的。在未来不能升级扩展的系统,会阻止存储器方面的人员运用可以降低功耗包络的功能和部件。不久前,我们还处在mm时代,现在则达到了nm时代,而pm节点也并非遥不可及。因此,可扩展性极为重要。目前,Qimonda正在从基于沟槽的技术转向混合型的技术。Qimonda的可扩展性已经超越了50nm和40nm节点,达到了约30nm的节点。这种可扩展性,使得Qimonda能够开发出核心平台,保证DRAM的低功耗特性。由于具有该平台,Qimonda现在能把产品放入各种具有音/视频功能的产品中。

评论