加速ASIC原型验证,Synopsys的HAPS-80提供高达100MHz性能

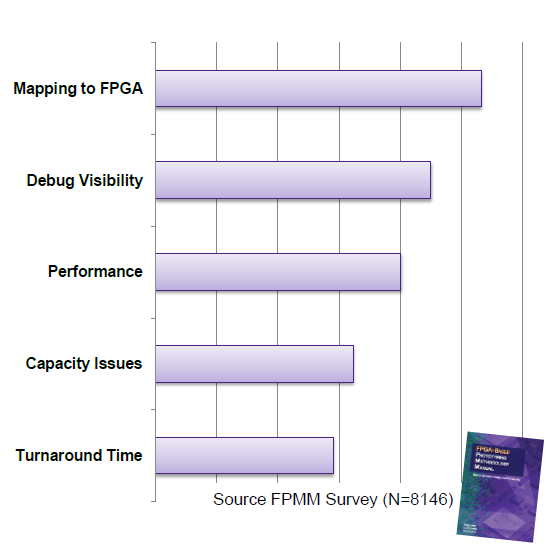

原型验证的挑战

现在做产品时,人们不仅关注ASIC本身,对软件平台更关注。因此设计送到Fab(芯片厂)生产之前,要做一些早期的原型认证。无论是ASIC设计者还是原型认证平台的开发者,现在关注两方面。

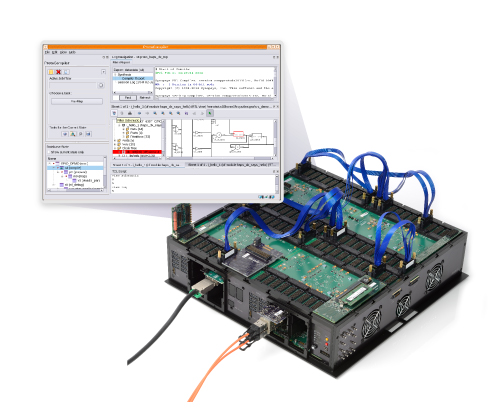

图:HAPS硬件和ProtoCompiler软件

首先是性能,最终产品可能要跑到GHz的频率,而且很多客户的项目时间越来越短,有些只有1年或6个月时间。在原型认证平台方面,人们期待高性能的软件开发,而目前市场上只是几十M、上百M赫兹的产品。

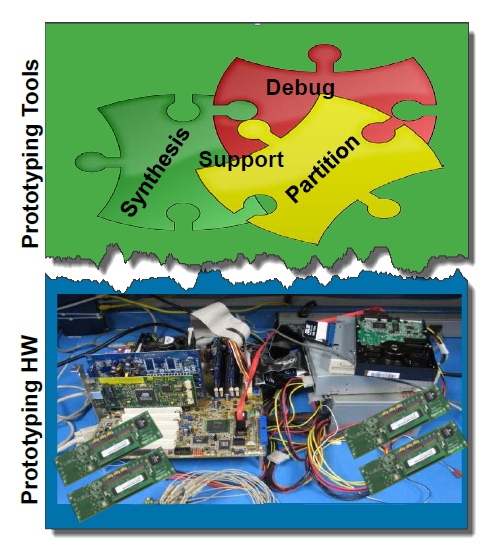

另外,产品要接近最终产品的真实性,所以现在从原型验证的需求上看,无论是软件工具还是硬件设备,市场上的产品组合很多也很复杂,所以如何选择也很重要。

图:市面上的物理原型产品组合多且复杂

Synopsys 资深产品市场经理Neil Songcuan先生称,Synopsys可以提供一站式的解决方案,不仅可以避免各种不确定性,而且集成化的HAPS硬件和ProtoCompiler软件将首款原型的完成时间缩短为不到2周。

HAPS-80优势分析

· 基于FPGA的HAPS-80原型系统结合ProtoCompiler软件,提供高达100MHz的多FPGA性能,以及全新的、自动化的引脚高速时分复用;

· ProtoCompiler软件专用于HAPS系统,自动化分区使首款原型的完成时间缩短为平均不到两周;

· HAPS-80企业级配置采用赛灵思(Xilinx)Virtex UltraScale FPGA芯片,可支持高达16亿个专用集成电路(ASIC)逻辑门,并支持面向并行设计执行的远程使用和多设计模式;

· 内置调试功能,能够捕获到数千个RTL信号,由工具自动插入,实现更高的调试效率和可见度;

· 作为Synopsys Verification Continuum平台的一部分,VCS仿真结合Unified Compile以及Verdi调试结合Unified Debug简化了在仿真、模拟和原型之间的移植,使设计和验证的启动时间缩短了数月。

HAPS-70时, ProtoCompiler软件已经提出了,此时的作用是什么?Neil Songcuan称承上启下,起到前后兼容的作用:使用户可以重用现存的HAPS-70子板和连接器。

自动化分区很重要吗?Neil Songcuan先生称,过去是手工分区,效率非常低下。而Synopsys提供了自动化分区方法,可大大提升效率。

为何采用Xilinx新一代芯片——Virtex UltraScale FPGA?众所周知,Xilinx的Virtex UltraScale FPGA是20nm芯片,Synopsys广受欢迎的上一代产品——HAPS-70采用的是Xilinx 28nm,并且采用了新型架构UltraScale芯片。Synopsys为何不把更多的28nm芯片累加,来实现更高的频率/速度?Neil Songcuan先生称过去为提高速度,已经采用了多个或十几个28nm芯片累加,但是仍然达不到理想速度。

老产品HAPS-70和HAPS-60还会继续销售吗?答案是老款产品仍将长期在市场上销售,以满足不同层次的芯片原型认证需要。

图:物理原型必需应对的挑战

HAPS-80的其他优势

“Synopsys使用了Xilinx前6代FPGA器件,是Xilinx在基于FPGA原型验证领域内的长期商业伙伴。Synopsys紧密集成了硬件和软件HAPS基于FPGA的原型解决方案,定位于从Virtex®UltraScale™ VU440器件提供最高性能和最大容量”Xilinx测试、测量和仿真市场业务部总监HannekeKrekels表示。“UltraScale芯片的器件密度提升了2.2倍,I/O增加了21%,它对于使用HAPS系统来实现多FPGA分区的复杂SoC原型是非常理想的。”、

与上一代产品相比,ProtoCompiler自动化从RTL到FPGA镜像的时序驱动流程,提供最高的原型性能和最快的迭代时间。ProtoCompiler以最优的多FPGA分区、最低的引脚时分复用比、优化的综合和引导式布局布线创建原型。这些特性使设计人员能够方便地利用HAPS-80的全部容量范围,高达16亿ASIC逻辑门。ProtoCompiler从IP到SoC的层次化流程,将RTL、设计原型约束、预定义的调试可观测点和逻辑综合指示封装在一起,以消除在SoC中重复这些任务的需求,将集成时间缩短了数周。

“Baikal-T1是世界上首款使用Imagination MIPS Warrior P5600 CPU实现的芯片,是我们致力于创新和高质量的结果,这得益于我们的研发中心采用了严格的硬件/软件集成和系统验证方法。我们依靠Synopsys的HAPS原型系统来提供高性能的ASIC原型,如为Baikal-T1提供的一个原型就在一个快速交付期限内准时完成,”贝加尔电子(Baikal Electronics)首席技术官Gregory Khrenov表示。“我们期待HAPS-80的众(诸)多特性为我们未来的工程项目带来益处。”

通过总是可用的第四代深度追踪调试技术(HAPS DTD4, HAPS Deep Trace Debug Gen4),HAPS-80系统提供了出色的调试可见度和自动化技术,通过它可在运行时从每个FPGA捕获超过1000个调试信号位。HAPS-80系统内置了调试数据采集、存储器和专用路由,且它们由ProtoCompiler自动插入以确保最小的干预,总是对用户可用。与Synopsys的Verdi™调试软件结合,HAPS DTD4可帮助设计人员以仿真器般的经验在原始RTL源文件的语境中,快速地辨识复杂的设计行为,使调试时间缩短多达50%。此外,HAPS和ProtoCompiler结合Verification Continuum的Unified Compile技术,使得在Synopsys VCS®仿真、ZeBu®模拟和HAPS原型之间移植更容易,从而可为设计和验证节省数月时间。

通用多源总线(UMRBus)的主机连接能力支持混合原型验证、全球可访问和大型原型群等使用模式。UMRBus在HAPS-80系统和Synopsys基于Virtualizer的虚拟原型之间无缝连接,为早期软件开发和硬件/软件集成创造了一种集成化的混合原型验证环境。此外,HAPS-80可向下兼容HAPS-70,让设计人员可复用现有的系统和硬件配件。对原生以太网连接的支持,使HAPS-80系统通过标准以太网连接便可实现系统的全球可访问。HAPS-80解决方案支持多设计模式,在企业配置中,可跨HAPS系统同时执行多个设计,为多项目用途提供最高的原型利用率及更高的投资回报率。

“我们优化每一代产品HAPS原型系统,提供最高的系统性能和设计人员生产率。新一代的HAPS-80系列解决了SoC设计人员在性能、可扩展性、首款原型完成时间和调试等方面的痛点,同时保持了与HAPS-70系统之间的互操作性,”Synopsys IP和原型营销副总裁John Koeter表示。“HAPS硬件和ProtoCompiler软件的独特结合,可在最短的时间实现最高性能的首款原型,以加速大型SoC及GPU设计的软件开发、硬件/软件集成和系统验证。”

供货和资源

HAPS-80基于FPGA的原型系统和ProtoCompiler软件现在已可供货。

有关HAPS-80的更多信息,请访问:

http://www.synopsys.com/Prototyping/FPGABasedPrototyping/Pages/haps-80.aspx

o 基于FPGA的原型技术博客:http://blogs.synopsys.com/breakingthethreelaws/

o ProtoCompiler: http://www.synopsys.com/Prototyping/FPGABasedPrototyping/Pages/protocompiler.aspx

o 混合原型构建:http://www.synopsys.com/Prototyping/FPGABasedPrototyping/Pages/hybrid-prototyping.aspx

o HAPS调试:http://www.synopsys.com/Prototyping/FPGABasedPrototyping/Pages/troubleshoot-debug.aspx

o 基于FPGA的原型构建方法学手册:http://www.synopsys.com/FPMM

评论