FPGA设计开发软件ISE使用技巧之:片上逻辑分析仪(ChipScope Pro)使用技巧

6.7 片上逻辑分析仪(ChipScope Pro)使用技巧

本文引用地址:https://www.eepw.com.cn/article/269338.htm在FPGA的调试阶段,传统的方法在设计FPGA的PCB板时,保留一定数量的FPGA管脚作为测试管脚。在调试的时候将要测试的信号引到测试管脚,用逻辑分析仪观察内部信号。

这种方法存在很多弊端:一是逻辑分析仪价格高昂,每个公司拥有的数量有限,在研发期间往往供不应求,影响进度;二是PCB布线后测试脚的数量就确定了,不能灵活地增加,当测试脚不够用时会影响测试,测试管脚太多又影响PCB布局布线。

ChipScope Pro是ISE下一款功能强大的在线调试工具。面对这些问题,ChipScope Pro都可以有效地解决。

6.7.1 ChipScope Pro概述

ChipScope Pro是针对Xilinx Virtex-II pro/ Virtex/ Virtex-II/ Virtex-EM/ Spartan-IIE/ Spartan-IIE 系列FPGA的在线片内信号分析工具。它的主要功能是通过JTAG口,在线实时读取FPGA的内部信号。

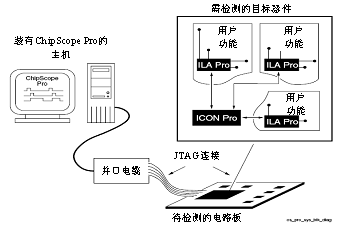

ChipScope Pro的基本原理是利用FPGA中未使用的BlockRam,根据用户设定的触发条件将信号实时地保存到这些BlockRam中,然后通过JTAG口传送到计算机,最后在计算机屏幕上显示出时序波形。ChipScope Pro应用的框图如图6.34所示。

图6.34 ChipScope Pro应用框图

其中ILA、ICON是为了使用ChipScope Pro观察信号而插入的核。ChipScope Pro工作时一般需要用户设计中实例化两种核:一是集成逻辑分析仪核(ILA core,Integrate Logic Analyzer core),该核主要用于提供触发和捕获的功能;二是集成控制核(ICON core,Integrated Contorller core),负责ILA core和边界扫描端口(JTAG)的通信。

一个ICON core可以连接1~15个ILA core。ChipScope Pro工作时,ILA core根据用户设置的触发条件捕获数据,然后在ICON core控制下,通过边界扫描端口上传到计算机,最后用ChipScope Pro Analyzer显示信号波形。

6.7.2 ChipScope Pro设计流程

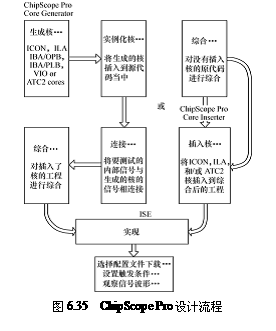

ChipScope Pro工具箱中包含了3个工具:ChipScope Pro Core Generator、ChipScope Pro Core Inserter、ChipScope Pro Analyzer,使用ChipScope Pro在线调试工具的FPGA设计流程如图6.35所示。

由上述流程可知,ChipScope Pro有两种使用方法。

第一种是由ChipScope Pro Core Generator根据设定条件生成在线逻辑分析仪IP核,包括ICON core、ILA core、ILA/ATC core和IBA/OPB core等,之后设计人员在原HDL代码中实例化这些核,然后进行综合、布局布线、下载配置文件,就可以利用ChipScope Pro Analyzer设定的触发条件,观察信号波形。

第二种是原代码完成综合后,由ChipScope Core Inserter工具插入ICON core和ILA core等核,它能自动完成在设计网表中插入这些核的工作,而不用手动在HDL代码中实例化这些核,在实际中应用的比较多,也是推荐大家使用的方法。下面就重点介绍ChipScope Pro Core Inserter和ChipScope Pro Analyzer的使用,这里以ChipScope Pro 8.2i为例来介绍。

fpga相关文章:fpga是什么

评论