DS-SS接收机全数字AGC的FPGA实现

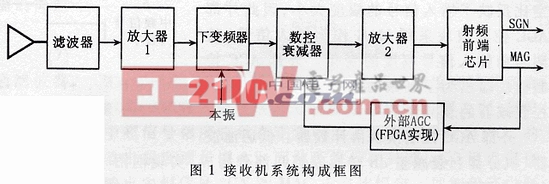

该DS-SS接收机系统构成如图1所示。其中射频前端采用NemeriX公司的NJ1004芯片,数控衰减器采用M/A-COM公司的AT90-0106。

1 外部AGC原理和设计

接收机的接收信号经过滤波器、放大器1和下变频器处理后,载波频率变为1575.42MHz,再经过数控衰减器和放大器2进入射频前端。在射频前端,NJ1004芯片内部对输入信号经过下边频、滤波、放大和AD采样后,输出SGN和MAG两路中频数字信号,AD采样位数为2bit,采样率为16.368MHz,中频信号频率为4.092MHz。射频前端NJ1004内部含有一个AGC系统,其动态范围为60dB。输入信号在射频前端的动态范围内变化时,SGN输出信号的占空比恒定为50%,MAG输出信号的占空比恒定为33.3%。

由于射频前端芯片内部AGC的动态范围不满足整个接收系统的工作要求,因此在接收机中增加一个外部AGC模块以保证接收机的动态范围。外部AGC控制模块的功能是检测出射频前端输出信号占空比变化而反映出来的接收信号幅度变化量,并通过低通滤波器滤出直流分量,经过一定的直流放大反馈给受控衰减器,调整输入信号幅度,使输入信号在放大器线性范围和射频前端AGC的调整范围之内,以达到恒定幅度输出的目的。

相关推荐

-

herbertwj | 2004-08-15

-

sandman555 | 2005-02-05

-

sandman555 | 2005-02-05

-

-

-

-

-

-

-

sandman555 | 2005-02-05

-

xiaohua | 2002-09-24

-

-

评论