DS-SS接收机全数字AGC的FPGA实现

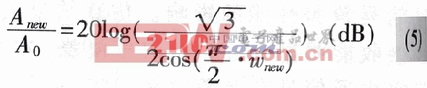

因此中频输出信号幅度与正常信号幅度的比值为:

由(5)式可以看出,中频输出连续信号幅度相对于正常信号幅度的比值与MAG端输出信号的占空比有关,因此AGC控制模块的关键是设计一个电路来检测输出信号的占空比。

利用一个计数器,采用射频前采样时钟16.368MHz作为计数时钟,在MAG高电平时计数。如果取计数时间为kms,则信号幅度处于射频前端动态范围之内时,正常的计数值为(k×10 -3×16.368×10 6)/3,记为n0。设接收信号幅度变大时,计数器的新计数值为n,则可推算出新的占空比为

wnew=n/3n0 (6)

由(5)和(6)式可知,已知新计数值和正常计数值就可计算出占空比,从而可计算出新的输入信号幅度与正常信号幅度的比值或对应分贝值。中频连续信号输出幅度相对于正常幅度的放大dB值正是AGC控制模块要输出给数控衰减器的数值,因此衰减值dB转换表就是基于(5)和(6)式构建的。要注意数控衰减器的衰减量并不是连续可调的。AT90-0106数字衰减器的衰减分辨率为1dB,最高衰减器为50dB.因此整个转换表也是以1dB为最小单位,将计数值(反映占空比)映射到衰减dB值。

评论