基于FPGA的SPI Flash控制器的设计方案

本文提出一个基于FPGA的SPI Flash读写硬件实现方案,该方案利用硬件对SPI Flash进行控制,能够非常方便地完成Flash的读写、擦除、刷新及预充电等操作,同时编写的SPI Flash控制器IP核能够进行移植和复用,作为SOC芯片的功能模块。SPI Flash控制器采用VHDL语言进行编写,在Modelsim 6.5g上通过功能仿真,并且在XUPV5-LX110TFPGA开发板上通过硬件测试,实现结果表明方案的可行性。

本文引用地址:https://www.eepw.com.cn/article/221568.htm1.引言

Flash是一种具有电可擦除的可编程ROM,按接口可以分为两大类:并行Flash和串行 Flash.并行Flash存储量大,速度快;而串行Flash存储量相对较小,但体积小,连线简单,可减小电路面积,节约成本。SPI Flash是内嵌SPI总线接口的串行Flash,它比起传统的并行总线接口Flash,节省了很多的I/O口资源,从而为系统功能的扩展提供了更多的可能。

随着SPI Flash越来越多地应用到各种领域,其传统读写方式中读写速度不够快、占用CPU资源以及操作不够简便灵活的缺点表现得更为突出,如何解决以上问题成为大家关注的焦点。利用硬件对SPI Flash进行控制,能够非常方便地完成Flash的读写、擦除、刷新及预充电等操作,且不占用CPU资源,同时编写的SPI Flash控制器IP核能够进行移植和复用,作为SOC芯片的功能模块。因此提出了一种基于FPGA的SPI Flash控制器的设计方案,并用VHDL实现。编写的SPI Flash控制器IP核在Modelsim 6.5g上进行了功能仿真,在FPGA开发板上进行了测试验证,可作为功能模块应用于SOC芯片设计。

2.SPI Flash控制器设计

2.1 SPI Flash芯片选择

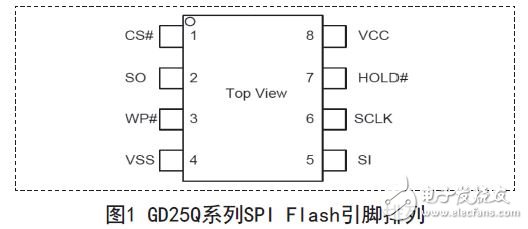

本方案SPI Flash芯片采用GigaDevice公司的GD25Q系列,GD25Q系列SPI Flash包括4Mbit的GD25Q40,2M bit的GD25Q20,1M bit的GD25Q10以及521K bit的GD25Q512,这里将采用512K bit的GD25Q512.图1为GD25Q系列SPIFlash(SOP8封装)引脚排列图。其中VCC和VSS分别为电源和地,其他6个引脚均可直接与F P G A的I / O引脚相连;写保护引脚W P #和HOLD#挂起引脚用于数据保护和空闲模式的低功耗运行,若不使用可将其置为高电平;CS#为片选信号,低电平时表示器件被选中,反之工作在待机状态;SO为串行数据输出,数据在时钟的下降沿输出到Flash器件;SI为串行数据输入,包括传输指令、地址和输入数据,输入信号在时钟的上升沿锁存到 Flash器件中。SCLK为串行时钟,由FPGA提供。

2.2 SPI Flash指令操作

GDQ25系列SPI Flash指令较多,所有指令都是8位,操作时先将片选信号CS#拉低选中器件,然后输入8位操作指令字节,串行数据在片选信号CS#拉低后的第一个时钟的上升沿被采样,SPI Flash启动内部控制逻辑,自动完成相应操作。有些操作在输入指令后需要输入地址字节和伪字节,最后操作完成后再将片选信号拉高。

2.3 SPI Flash控制器设计原理

SPI Flash控制器必须能够产生SPI Flash芯片执行各操作(如写使能、刷新、预充电、读芯片ID、读取状态寄存器、写状态寄存器、扇区擦除、块擦除、整体擦除、读取数据、快速读取数据、页面编程)时所需指令时序,用户只需要输入对应操作的8位指令值及对应的操作地址值,SPI接口与SPI Flash的数据传输将由SPI Flash控制器内部状态机控制执行。

3.SPI Flash控制器实现

3.1 SPI Flash测试系统

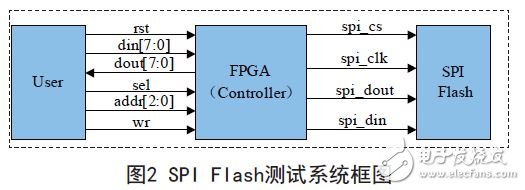

本文设计的SPI Flash测试系统由用户端、FPGA和SPI Flash构成,系统框图如图2所示,其中FPGA选用Xilinx公司Virtex5系列芯片(Virtex-5 XC5VLX110T),SPI Flash芯片采用GigaDevice公司的GD25Q系列512K bit容量的GD25Q512.

SPI Flash控制器由VHDL编写,主要为SPIFlash芯片提供串行时钟,将从用户端输入的数据(包括指令字节、地址字节和数据字节)寄存起来并在串行时钟的控制下通过spi_dout信号线逐位输出到SPI Flash芯片中,同样将从SPI Flash芯片中读出的串行数据转换成并行数据送给用户端。此外,SPI Flash控制器还必须在用户通过sel、addr以及wr组合发出的操作命令下产生一系列的控制信号,并在这些控制信号的作用下根据状态机的转换方向进行动作并且输出相应的结果。

fpga相关文章:fpga是什么

评论