将数据转换器IP集成到系统芯片简化设计技术(二)

当数据转换器需要外部基准时也会出现类似的问题。由于基准决定数据转换器的满幅输入摆幅,如果噪声或不需要的信号与基准耦合,就会成为数据转换器输出信号的一部分。

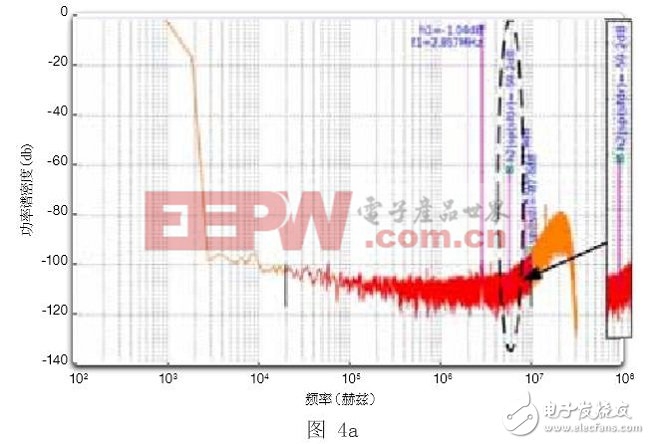

图 4a显示了28纳米12位Sigma-DeltaIQ模拟-数字转换器频谱,可以看到转换器输入与基准信号之间有耦合。这会导致第二谐波(h2)能量过大,将总谐波失真(THD)降低近14dB。相反,图4b显示的是相同IQ模拟-数字转换器在耦合消除后的性能,这会使总谐波失真改善,达到 -72dBc。

基准对流经非零电阻(电阻压降)基准路径的非零电流造成的压降很敏感。这一效应会在转换中产生系统性的偏移(offset)和增益误差(gain error)。

考虑到这些影响,将数据转换器正确植入系统芯片之后,下一步就是对转换器和I/O之间的模拟信号进行布线,同时采用以下技术:

技术3:保持模拟布线路径简短

保持模拟布线路径尽可能简短,使无关信号不太可能耦合到模拟I/O出或基准中。

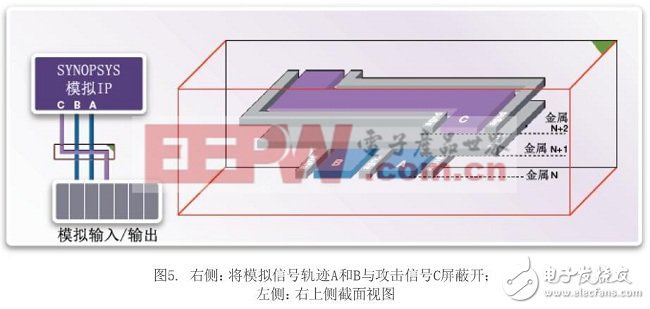

技术4:增加屏蔽

为尽可能减少关键模拟信号的噪声耦合或串扰,特别是在串扰无法避免的情况下,设计人员应在攻击者和受害者轨迹之间增加屏蔽。图5介绍了增加有效屏蔽的正确方法:通过中间层(金属N+1)将以金属N布线的模拟信号轨迹A和B与以金属N+2布线的噪声信号C屏蔽开来,完全覆盖重叠区域,并与干净的模拟接地电源连接。通过在临近信号增加金属层走线,可在同层的金属间(分别是金属N与N+2)实现进一步屏蔽隔离。

只有在必须的情况下才增加屏蔽,而且是不沿着所有路径,以避免不必要地增加信号寄生电容。

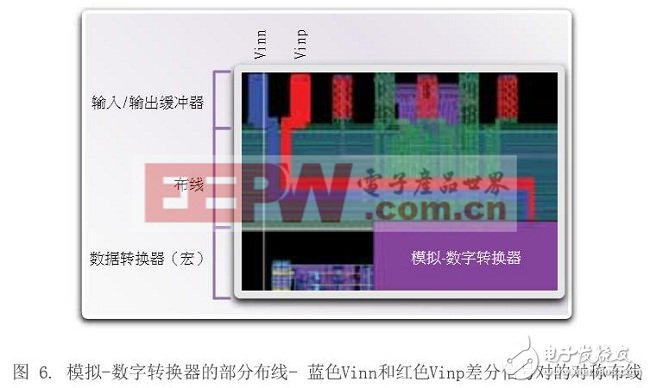

技术5:保持差分走线

为确保模拟差分信号的共模噪声抑制达到最佳效果,设计师应根据电阻、长度、电容性负载和其他信号的寄生电容耦合、邦定线特征和印刷电路板(PCB)线路等等,对差分信号布线匹配。图6是从模拟-数字转换器到I/O匹配后的输入(红色Vinp和蓝色Vinn)布线。

技术6:限制电阻压降或阻抗

可通过以下方式确保布线串联电阻不超过数据转换器提供商注明的最大电阻值:

△尽量缩短布线距离

评论