将数据转换器IP集成到系统芯片简化设计技术(二)

△尽量使用多个金属层走线

△使用大量过孔进行连接

数字输出/输入布线还要求认真仔细地部署。但是,由于布线是在自动数字集成流程中处理,它们的部署自然需要遵循相应的技术,因此不在本文讨论之列。

3. 保持低时钟抖动

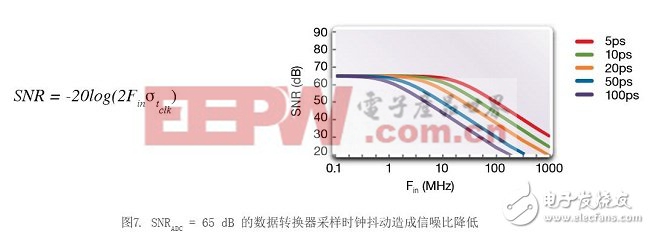

基于数据转换器的系统性能,如通讯接口,取决于采样时钟的质量。模拟-数字转换器信号采样瞬间的不确定性增加了转换噪声,因而降低了转换器性能。采样瞬间的不确定性称为“抖动”。时钟抖动(σtclk)决定了数据转换器可达到的最大理论SNR(信噪比)值。图7显示信噪比是采样时钟抖动的一个函数,将信噪比、时钟抖动和信号频率(Fin)关联起来。以模拟-数字转换器固有的65dB信噪比(SNRADC)为例。

从图7可以看出,采样时钟抖动对转换性能(信噪比)的影响与系统处理低频率信号无关。但是,采样时钟抖动的影响随着所处理信号的频率增强而增加

因此,系统芯片设计师在设计中必须考虑到这种影响,可以采用以下技术保证采样时钟质量:

技术7:将时钟源靠近数据转换器

将锁相环靠近数据转换器,可降低外部信号耦合到时钟线并造成时钟抖动的可能性。

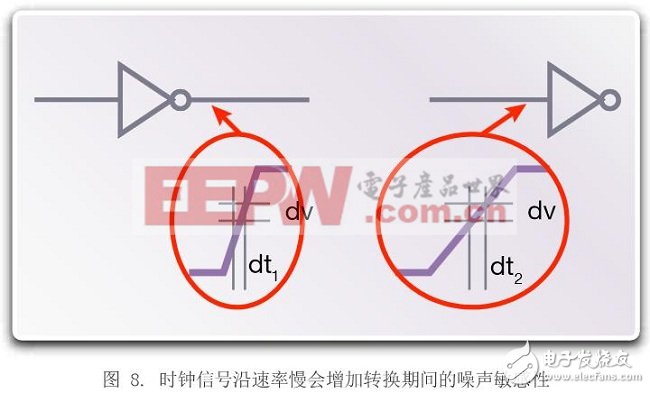

技术8:检查时钟沿速率

对于时钟路径上的任何电路而言,应保证有足够的驱动强度限制时钟的转换速率。时钟沿转换时间长会增加噪声敏感性,因而增加抖动(如图8所示)。根据经验,~100ps的转换时间是适当的。

评论