构建节能AI加速器的硬件策略有哪些?

人工智能 (AI) 应用每天都在扩展到更多行业。然而,这些人工智能系统使用的能源量已成为一个重大问题。现代深度神经网络需要大量的计算能力。

本文研究了构建节能 AI 加速的五种关键硬件策略:专用加速器架构、模拟内存计算、异构计算系统、神经形态计算和 3D 芯片堆叠技术。

专用加速器、硬件架构

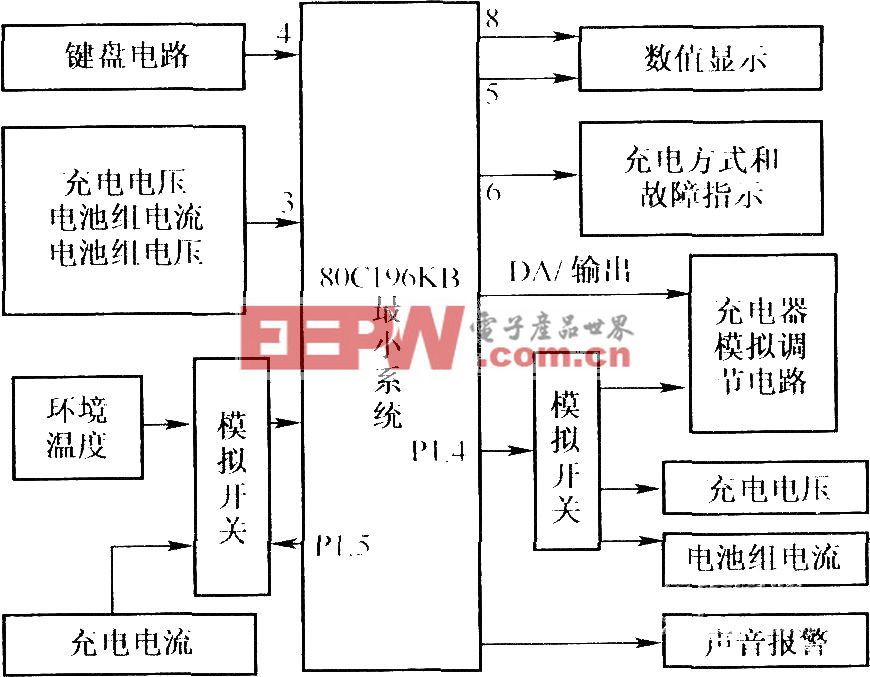

人工智能系统需要特殊的计算机芯片,在运行人工智能模型时,这些芯片比普通 CPU 工作得更好。普通 CPU 无法足够有效地处理 AI 任务并消耗过多的功率。为了解决这个问题,工程师们创建了四种主要类型的专用加速器架构,如图 1 所示。每种类型的硬件加速器都有其优势,最适合不同类型的 AI 工作负载:

图 1.不同的专用 AI 加速器硬件架构。(图片来源:AI加速器研究院)

图 1.不同的专用 AI 加速器硬件架构。(图片来源:AI加速器研究院)

图形处理单元 (GPU) 具有数千个具有高内存带宽的并行计算核心,使其成为深度学习中常见的矩阵运算的理想选择。他们的架构包括专门的张量核心,可以加速人工智能作,同时保持跨各种框架的灵活性。

神经处理单元 (NPU) 专为 AI 推理而设计,具有针对矩阵乘法和卷积运算优化的多个计算单元。它们的架构包括片上存储器,以减少数据传输开销并提高吞吐量,尤其是在卷积神经网络方面表现出色。

现场可编程门阵列 (FPGA) 提供数百万个可编程门,可针对特定 AI 任务进行重新配置。这种灵活性允许优化特定的神经网络架构,同时实现低延迟,使其对实时应用程序很有价值。

专用集成电路 (ASIC) 通过专门为特定人工智能模型量身定制的定制设计架构提供最高的能源效率。虽然缺乏灵活性,但它们为专用应用提供了卓越的每瓦性能。

每种架构都代表了灵活性、性能和能源效率之间的不同权衡,允许开发人员根据其特定的 AI 推理要求和部署限制选择最佳硬件策略。

模拟内存计算架构

模拟内存计算 (AIMC) 通过在存储数据的地方执行计算来解决冯·诺依曼瓶颈,而不是在单独的处理单元和内存单元之间移动信息。图 2 说明了相变存储器 (PCM) 器件如何通过利用基本物理原理的交叉阵列实现这种方法。

图 2.模拟内存计算的工作原理。显示了从基本存储设备到可以直接在内存中运行不同类型神经网络的完整系统的进展。(图片来源:ResearchGate)

矩阵向量乘法是神经网络中的主要运算。这些作使用欧姆定律和基尔霍夫定律执行。施加到字线的输入电压与存储的电导值相互作用,产生与所需计算结果成正比的电流。

AIMC tile 架构集成了数模转换器和模数转换器。这些组件与数字系统接口,同时保持模拟计算效率。这种方法通过消除数据移动开销并实现显着的并行性(同时执行数百万个作)来提供能源优势。

非易失性存储器特性进一步降低了静态功耗。ALPINE 框架在多种神经网络类型(例如 MLP、CNN、RNN 和 LSTM)中展示了这些优势。与传统实施相比,它可以实现高达 20.5 倍的性能加速和 20.8 倍的能源改进。然而,在管理精度限制和设备可变性方面仍然存在挑战。

异构计算架构

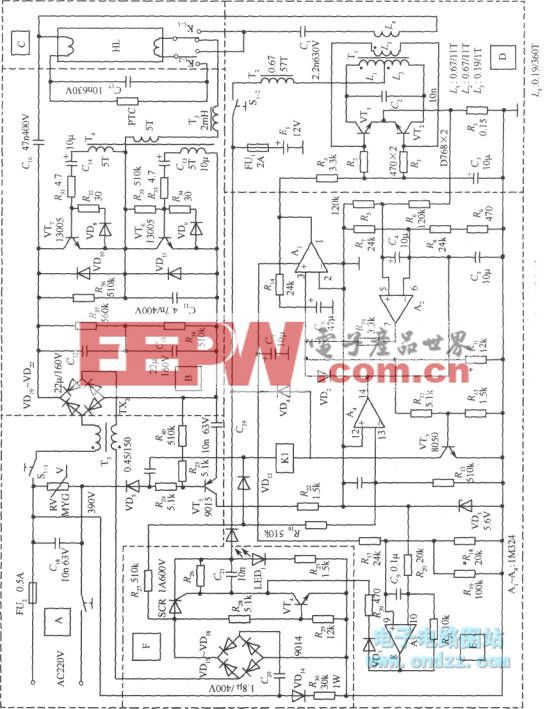

异构计算架构通过部署多个专用处理单元来协同处理人工智能工作负载的不同方面,从而提高能源效率。图 3 说明了瑞萨电子的 DRP-AI3 实现,其中 AI 加速器与动态可重构处理器 (DRP) 和传统 CPU 内核一起工作。这种方法认识到人工智能应用程序需要不同的计算模式。这些范围从神经网络推理到基于算法的处理和系统控制。每种模式都针对不同的硬件类型进行了优化。

图 3.用于异构架构中 AI 任务的专用硬件,用于其他算法的可配置硬件,以及用于系统控制的常规处理器。(图片来源:瑞萨电子)

图 3.用于异构架构中 AI 任务的专用硬件,用于其他算法的可配置硬件,以及用于系统控制的常规处理器。(图片来源:瑞萨电子)

AI 加速器组件使用专用 MAC 单元和优化的数据流处理计算密集型神经网络作,而可重新配置的 DRP 处理器动态调整其电路配置以进行流数据处理、图像预处理和池化作。CPU 管理系统级任务并提供编程灵活性。

这种分工使每个处理单元能够在其专业领域内高效运行,从而避免了与强制通用硬件处理专门任务相关的能源损失。合作设计取得了显着的成果,硬件与软件的协调提供了高达 10 倍的性能提升,同时保持了对不同 AI 模型类型的灵活性。

跨异构组件的多线程流水线进一步优化了资源利用率,展示了战略任务分区如何提高整体系统能效。

神经形态计算

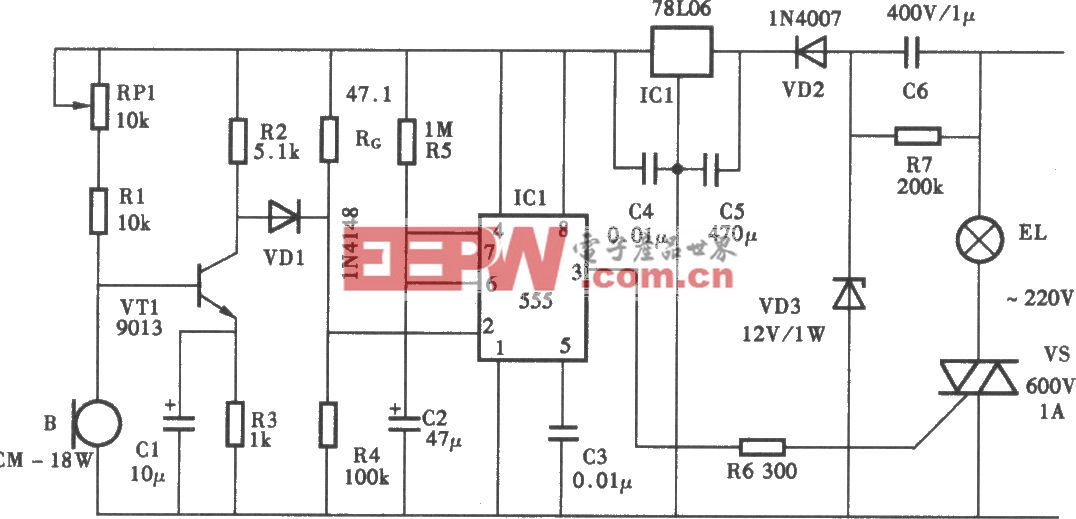

神经形态计算复制了人脑使用能量的方式。这种受大脑启发的方法通过使用忆阻器作为电子突触来改变我们构建计算机的方式。这些忆阻器结合了处理和存储器通常单独执行的工作。图 4 显示了三维神经形态架构如何构建分布式计算网络。在这些系统中,忆阻器件同时用作存储和计算元件。这种方法创建了非冯诺依曼系统,其工作方式与普通计算机非常不同。

图 4.显示 (a) 2D 神经网络,(b) 3D 实现,(c) 神经元-突触连接的 3D 神经形态系统。(图片:IntechOpen)

与传统的 2D 方法相比,3D 实现具有优势,因为它在神经元层之间提供高连接性,同时解决影响传统设计的路由拥塞问题。忆阻突触能够通过自适应学习能力实现并行数据处理,以类似于生物神经网络的事件驱动方式处理信息。

该架构支持各种神经形态计算方法,包括分布式、集中式和自适应神经形态计算架构。

调查数据表明,尖峰神经网络加速器表现出更高的能效,平均消耗 0.9 瓦,而非尖峰实现的平均功耗为 1.7 瓦。它使神经形态计算非常适合需要智能、自适应行为的低功耗边缘应用。

3D芯片堆叠

三维芯片堆叠解决了平面半导体缩放的物理限制,同时通过缩短互连距离来提高能效。图 5 说明了两种主要的 3D RRAM 集成策略:水平 3D RRAM (H-RRAM) 和垂直 3D RRAM (V-RRAM) 结构,它们将传统的 2D 横杆阵列扩展到三维空间。这种垂直缩放通过面积缩放实现了器件密度的显着提高。

图 5.3D 芯片堆叠架构可提高器件密度和能效。(图片来源:ResearchGate)

能效提升源于缩短的信号路径和减少的互连电容,直接降低了功耗,同时实现了高连接性系统。硅通孔促进层间通信,创建适合密集神经网络实现的并行数据处理能力。

随着层数的增加,V-RRAM架构被证明特别具有成本效益。临界光刻掩模的数量仍然相对独立于堆叠层。这与 H-RRAM 不同,H-RRAM 的模板要求是线性扩展的。这种 3D 方法允许将内存和处理元素组合到一个块中。这使得神经网络加速器具有更高的密度和更高的能效,适用于需要紧凑性和速度的下一代人工智能应用。

总结

构建节能的 AI 加速器包括许多硬件策略。这些范围从专用架构和模拟内存计算到异构系统、神经形态设计和 3D 集成技术。人工智能加速的未来在于巧妙地结合各种技术。成功将取决于硬件-软件协同设计。这意味着算法优化和硬件能力必须同步发展,以提高人工智能系统的能源效率。

评论